# Bias Temperature Instability Modelling and Lifetime Prediction on Nano-scale MOSFETs

Rui Gao

A thesis submitted in partial fulfilment of the requirements of Liverpool John Moores University for the degree of Doctor of Philosophy

July 2018

### Acknowledgements

First I would like to express my greatest gratitude to my first supervisor Dr. Zhigang Ji for his continuous support, guidance and encouragement throughout my entire PhD research project.

I would also thank my second supervisor Prof. Jianfu Zhang and third supervisor Prof. Weidong Zhang for the fruitful discussions which made the project much more efficient. Thanks to Dr. Benbakhti Brahim for reviewing my transfer report.

I want to thank all the members working together (used to work) in LJMU microelectronics reliability and characterization group. They are: Dr. Meng Duan, Dr. Jigang Ma, Dr. Zheng Chai, Mr. Xiong Zhang, Mr. Azrif Manut, Dr. Pengpeng Ren, Mr. Steven Duffy, Mr. James Brown, Mr. Dale Hodgkinson and Ms. Mehzabeen Mehedi. Dr. Meng Duan's pioneering work on variability and Dr. Jigang Ma's outstanding work on *Energy Alternating Defects* laid a solid foundation for the modelling work in this project. Dr. Jigang Ma also helped me a lot to improve my electric characterization skills in my first year.

Thanks to Mrs. Helen Pottle, Mrs. Caroline O'Rourke for helping me out when my scholarship was delayed.

Last, but not least, I would like to express my deepest love to my family.

### Abstract

Bias Temperature Instability (BTI) is one of the most important reliability concerns for Metal Oxide Semiconductor Field Effect Transistors (MOSFET), the basic unit in integrated circuits. As the development MOSFET manufacturing technology, circuit designers need to consider device reliability during design optimization. An accurate BTI lifetime prediction methodology becomes a prerequisite.

Typical BTI lifetime standard is ten years, accelerated BTI tests under high stress voltages are mandatory. BTI modelling is needed to project BTI lifetime from high voltages (accelerated condition) to operating voltage. The existing two mainstream BTI models: 1). The Reaction-Diffusion (R-D) framework and 2). The Two-Stage model cannot provide accurate lifetime prediction. Quite a few fitting parameters and unjustifiable empirical equations are needed in the R-D framework to predict the lifetime, questioning its predicting capability. The Two-stage model cannot project device lifetime from high voltages to operating voltage.

Moreover, the scaling down of MOSFET feature size brings new challenges to nano-scale device lifetime prediction: 1). Nano-scale devices' current is fluctuating due to the impact of a single charge is increasing as MOSFET scaling down, repetitive tests need to be done to achieve meaningful averaged results; 2). Nano-scale devices have significant Device-to-Device variability, making the lifetime a distribution instead of a single value.

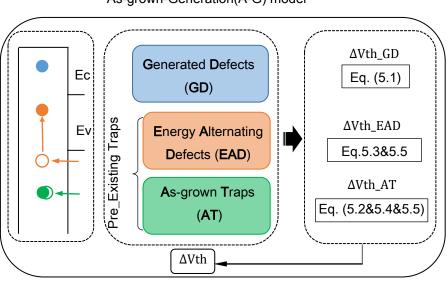

In this work a comprehensive As-grown Generation (A-G) framework based on the A-G model and defect centric theory is proposed and successfully predicts the Time Dependent Variability and lifetime on nano-scale devices. The predicting capability is validated by the good agreement between the test data and predicted values. It is speculated that the good predicting capability is due to the correct understanding of different types of defects.

In the A-G framework, Time Dependent Variability is experimentally separated into Within-Device Fluctuation and the averaged degradation. Within-Device Fluctuation can be directly measured and the averaged degradation can be modelled using the A-G model. The averaged degradation in the A-G model contains: Generated Defects, As-grown Traps and Energy Alternating Defects. These defects have different kinetics against stress time thus need separate modelling. Various patterns such as Stress-Discharge-Recharge, multi-Discharging-based Multiple Pulses are designed to experimentally separate these defects based on their different charging/discharging properties. Fast-Voltage Step Stress technique is developed to reduce the testing time by 90% for the A-G framework parameter extraction, making the framework practical for potential use in industry.

| Abbreviations | Signification                                                  |

|---------------|----------------------------------------------------------------|

| A(H/E)T       | As-grown (Hole/Electron) Traps                                 |

| A-G model     | As-grown Generation model                                      |

| AN(PC/ET)     | Anti-Neutralization (Positive Charges/Electron Traps)          |

| CET           | Capture Emission Time                                          |

| СР            | Charge Pumping                                                 |

| CPC/CET       | Cyclic Positive Charges/Cyclic Electron Traps                  |

| CV            | Capacitance-Voltage                                            |

| EAD           | Energy Alternating Defects                                     |

| EoS/EoR       | End of Stress/End of Recovery                                  |

| ЕоТ           | Effective Oxide Thickness                                      |

| Freq          | Frequency                                                      |

| IV            | Drain current (I <sub>d</sub> )~Gate voltage (V <sub>g</sub> ) |

| Meas          | Measurement                                                    |

| MOS(FET)      | Metal Oxide Semiconductor (Field Effect Transistor)            |

| MSM           | Measure-Stress-Measure                                         |

| N/PBTI        | Positive/Negative Bias Temperature Instability                 |

| Pts           | Points                                                         |

| R-D model     | Reaction-Diffusion model                                       |

| RTN           | Random Telegraph Noise                                         |

| SDR           | Stress-Discharge-Recharge                                      |

| SMU           | Source Measure Unit                                            |

| SR            | Sampling Rate                                                  |

| T0V/TDV       | Time-zero Variability/Time Dependent Variability               |

| TDDS          | Time Dependent Defect Spectroscopy                             |

| UE/LE         | Upper Envelope/Lower Envelope                                  |

| VRS           | Voltage Ramp Stress                                            |

| (F-)VSS       | (Fast-) Voltage Step Stress                                    |

| WDF           | Within Device Fluctuation                                      |

## **List of Abbreviations**

| Symbol                           | Description                                     | Unit             |

|----------------------------------|-------------------------------------------------|------------------|

| C <sub>ox</sub>                  | oxide capacitance                               | F                |

| E <sub>a</sub> '                 | activation energy                               | eV               |

| Ec                               | bottom of the conduction band                   | eV               |

| $E_{f}/E_{F}$                    | Fermi level                                     | eV               |

| $E_{v}$                          | top of the valence band                         | eV               |

| g <sub>m</sub>                   | transconductance of an $I_d$ - $V_g$ curve      | S                |

| I <sub>d</sub>                   | drain current                                   | А                |

| $I_{doff}$                       | "off" state drain current                       | А                |

| I <sub>dcc</sub>                 | constant $I_d$ value for $V_{th}$ extraction    | А                |

| Ig                               | gate leakage current                            | А                |

| N <sub>c</sub>                   | effective density of states in conduction band  | cm <sup>-3</sup> |

| N <sub>IT</sub> /N <sub>it</sub> | interface states density                        | cm <sup>-3</sup> |

| $N_v$                            | effective density of states in valence band     | cm <sup>-3</sup> |

| Т                                | Temperature                                     |                  |

| $T_{w}$                          | time window                                     | S                |

| $V_{dd}$                         | drain supply voltage /Circuit operating voltage | V                |

| $V_{g}$                          | gate voltage                                    | V                |

| $V_{gch}$                        | charging gate voltage                           | V                |

| $V_{gdisch}$                     | discharging gate voltage                        | V                |

| $V_{grech}$                      | recharging gate voltage                         | V                |

| $V_{gst} / V_{gstress}$          | stress gate voltage                             | V                |

| $V_{th}$                         | threshold voltage                               | V                |

| W/L                              | MOSFET channel width/length                     | m                |

| $\Delta V_{th}$                  | threshold voltage shift                         | V                |

| $\sigma_i$                       | capture cross section                           | cm <sup>-2</sup> |

| $arphi_{ m s}$                   | surface potential                               | eV               |

# List of Symbols

# **List of Figures**

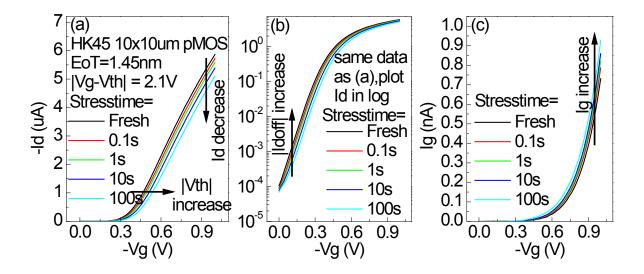

| Fig. | 1.1 MOSFET $I_d$ - $V_g$ (IV) curves show both $ V_{th} $ (a) and $ I_{d_off} $ increases under NBTI stress. (c) $I_g$ - $V_g$ measurements show gate leakage ( $I_g$ ) also increases 2                                                                                                                                                                                                                                             |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. | 1.2 (a) Illustration of the operation condition of a CMOS inverter in circuits. (b) With input 0/1 (GND/V <sub>dd</sub> ), output is $1/0$ (V <sub>dd</sub> /GND) and the pMOS/nMOS device (top/bottom) is under uniform negative/positive gate bias towards its bulk in the marked phases                                                                                                                                           |

| Fig. | 1.3 Names and locations of charges associated with thermal oxidized silicon [3].                                                                                                                                                                                                                                                                                                                                                     |

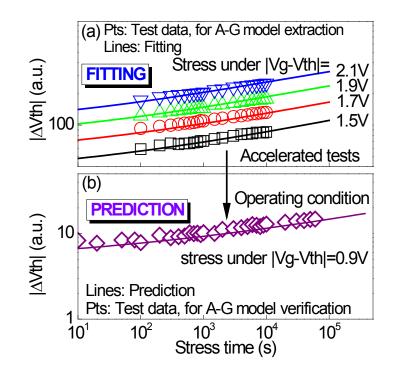

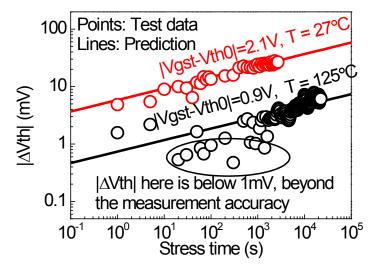

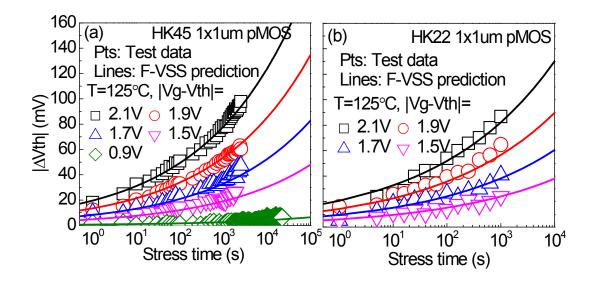

| Fig. | 1.4 An example of BTI lifetime projection from accelerated tests to operating condition. (a) Test data under high $ V_g-V_{th} $ (accelerated stress) condition is used to extract model parameters and predict device lifetime. (b) The accuracy of the prediction is usually verified by the comparison of test data under use-bias and model prediction. Note the test data in (b) should not be used to extract model parameters |

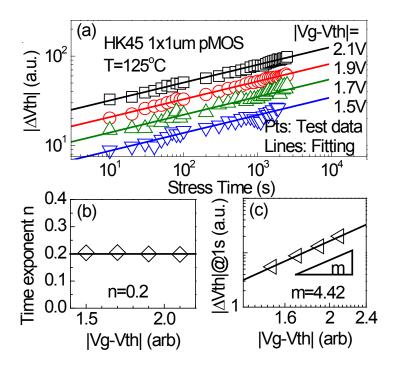

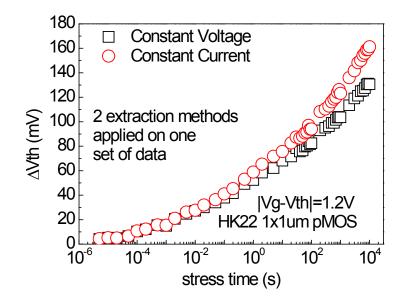

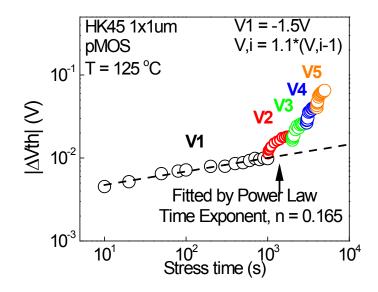

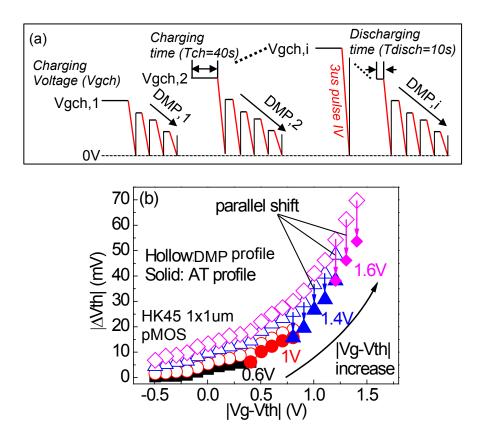

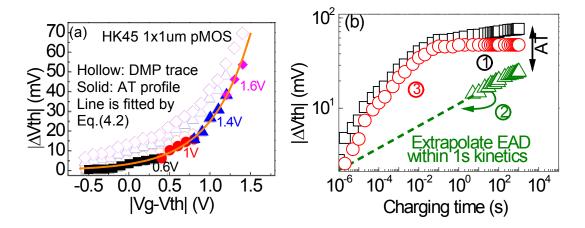

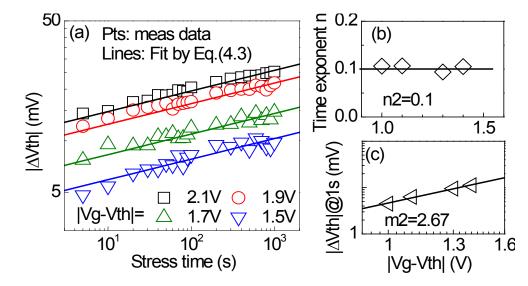

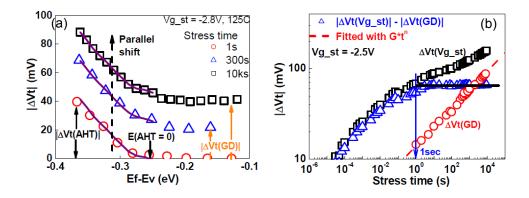

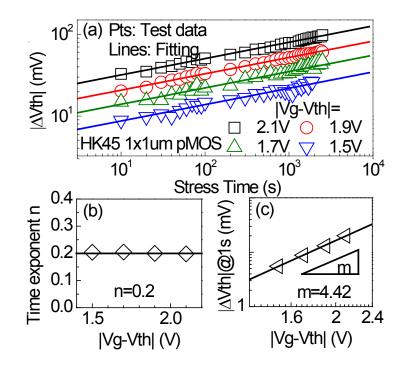

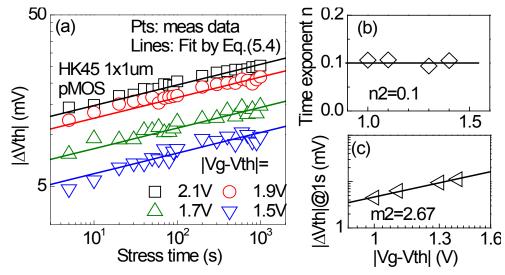

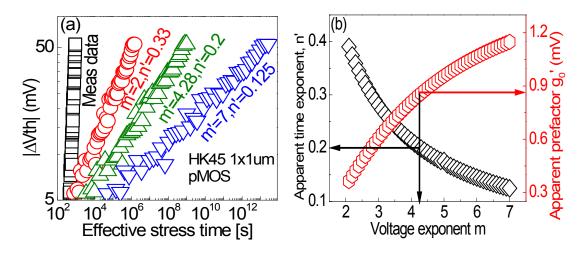

| Fig. | 1.5 BTI kinetics measured by the slow DC characterization can be well described by Equation (1.1). NBTI is adopted as an example here. $ \Delta V_{th} $ kinetics under different $ V_g-V_{th} $ stress (a) can be well fitted by power law with the same time exponent n (b), $ V_g-V_{th} $ power exponent m can then be extracted from fitted $ \Delta V_{th} @$ 1s against $ V_g-V_{th} $ (c)                                    |

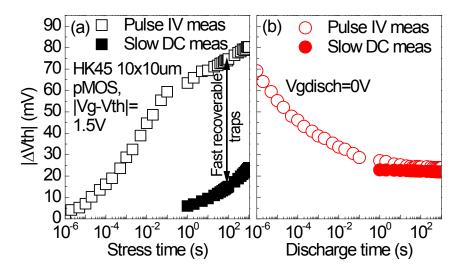

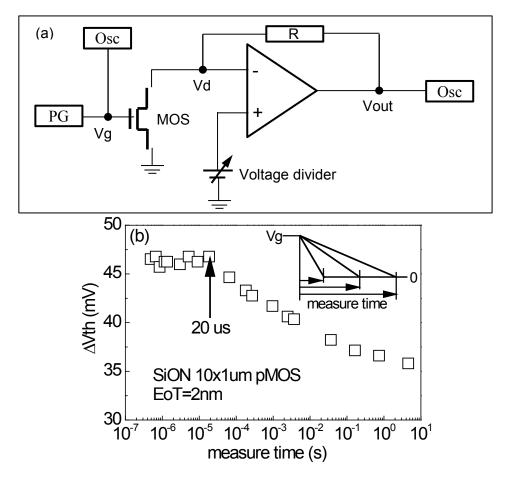

| Fig. | 1.6 NBTI stress (a) and recovery (b) kinetics measured by fast pulse IV measurement and slow DC measurement. For each data point, the hollow one is measured in 3 microseconds while the solid one is measured in 100 milliseconds. Slow DC measurement only captures the slow traps induced $ \Delta V_{th} $ thus underestimates the total $ \Delta V_{th} $ . Refer to section 2.3 for details                                    |

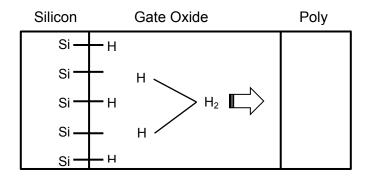

| Fig. | 1.7 Schematic illustration of the R-D model to interpret interface trap generation                                                                                                                                                                                                                                                                                                                                                   |

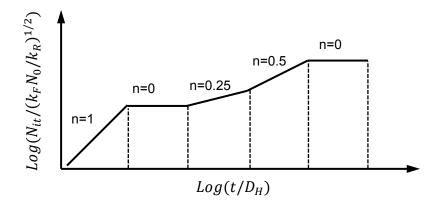

| Fig. | 1.8 Five phases obtained from the general solution of the R-D equations during NBTI stress                                                                                                                                                                                                                                                                                                                                           |

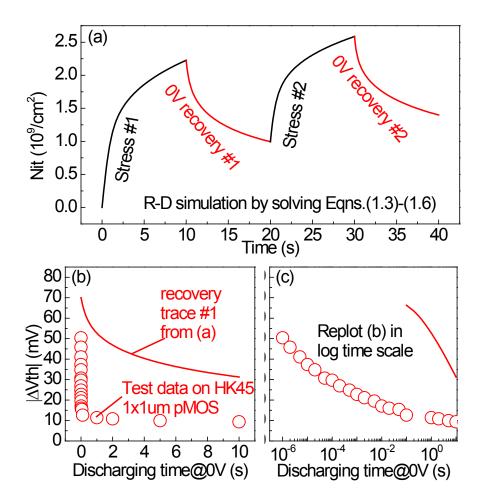

| Fig. | 1.9. (a) The R-D model based simulation of a BTI stress-recovery-stress procedure. (b) Test data on HK45 1x1um pMOS. (c) Plot the data from (b) in log scale. It's unlikely that almost half of the hydrogen diffused in 10 seconds will diffuse back in less than 1 millisecond. 14                                                                                                                                                 |

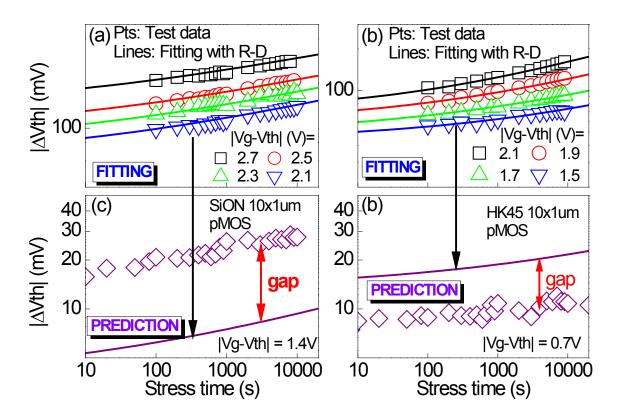

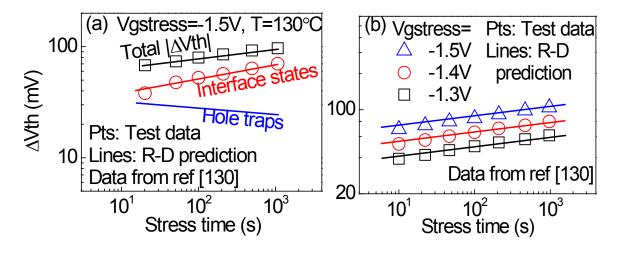

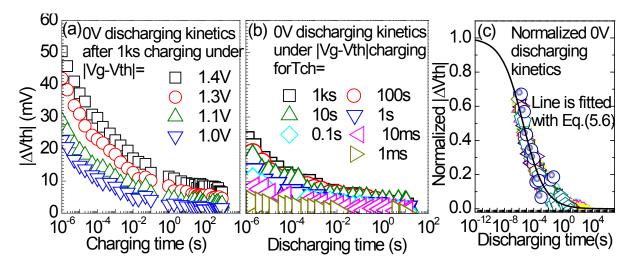

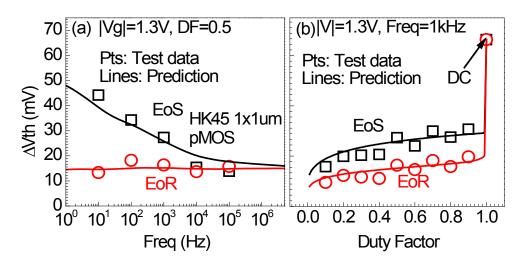

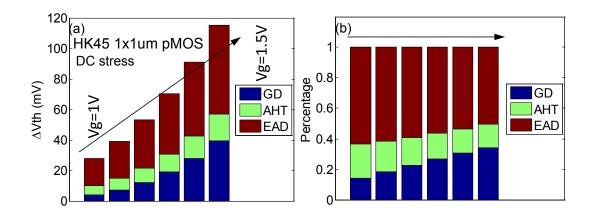

| Fig. | 1.10 The R-D framework prediction on 2 different processes of pMOSFETs. Parameters are extracted by fitting the experiment data and R-D framework prediction (upper), however they cannot predict the NBTI behavior under a much lower voltage (lower)                                                                                                                                                                               |

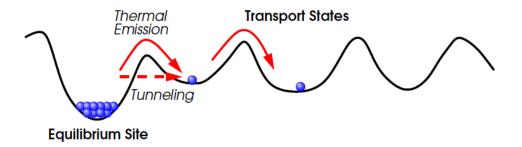

| Fig. | 1.11 The Si-H dissociation from energy-levels perspective. Hydrogen is released from a Si-H bond over a barrier into transport states (tetrahedral interstitial sites,                                                                                                                                                                                                                                                               |

|      | bond center sites, etc.). Emission may occur via thermal emission or, at very low temperatures, via tunneling [46]                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

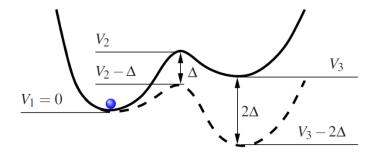

| Fig. | 1.12. Impact of the electric field on energy level in double well model. In equilibrium, the first well $(V_1)$ is the energetically preferred configuration, application of the electric field tilts the wells favoring the second well $(V_3)$ [46].                                                                                                                                                                                                                                                                                                                                     |

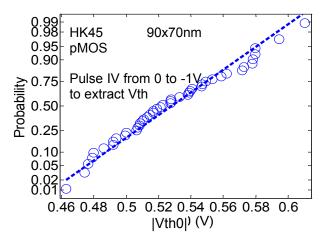

| Fig. | 1.13 Fresh threshold voltages $ V_{th0} $ measured on 50 HK45 90x70nm pMOSFETs follow a normal distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

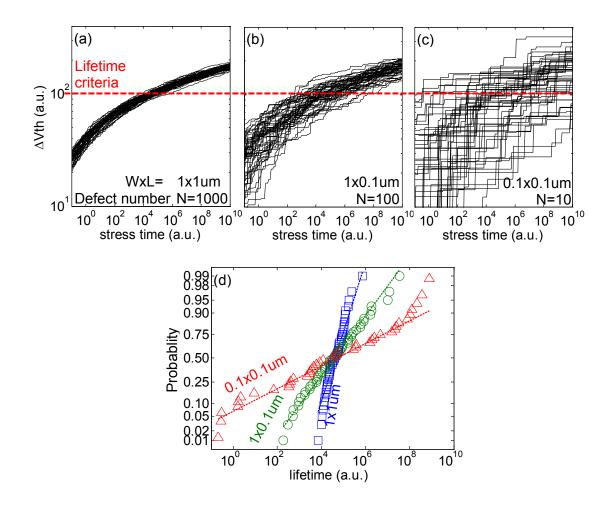

| Fig. | 1.14 Simulated BTI kinetics against stress time on different size of pMOSFETs (a-c) based on the defect centric theory in [50]. 50 devices are simulated for each size, a criteria of $ \Delta V_{th} $ =100 is adopted to extract the lifetime of all 50 devices and their distributions are plotted in (d). It is clearly shown that as device size scaling down, Device-to-Device Variability of BTI kinetics becomes larger, resulting in a wider spreading in lifetime for each device. This is because large device contains many defects and their random properties average out 22 |

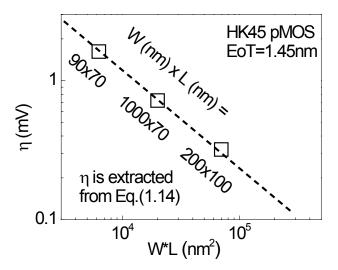

| Fig. | 1.15 Average impact of a single defect ( $\eta$ ) values extracted on 3 different sizes of HK45 pMOSFETs show an inverse proportional relation against device area W*L.                                                                                                                                                                                                                                                                                                                                                                                                                    |

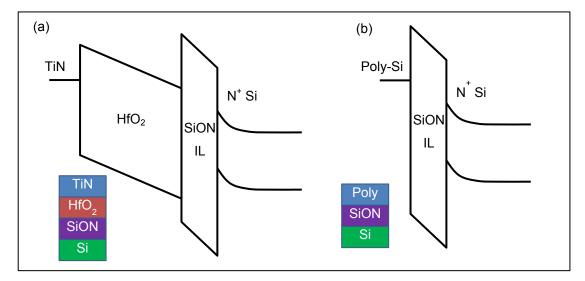

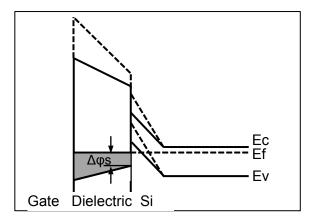

| Fig. | 2.1 Device structure and the corresponding energy band diagram during NBTI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| -    | stress condition of High-k Metal Gate (a) and Poly-Si Gate SiON (b)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

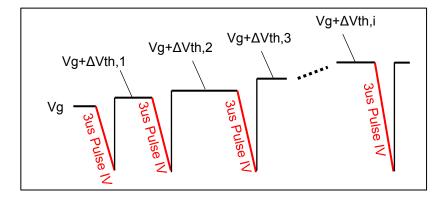

| г.   | milliseconds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

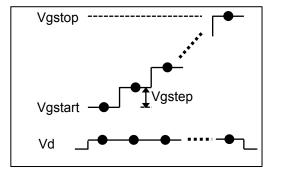

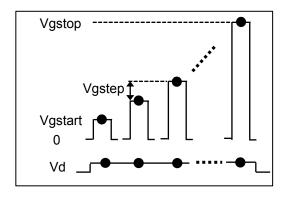

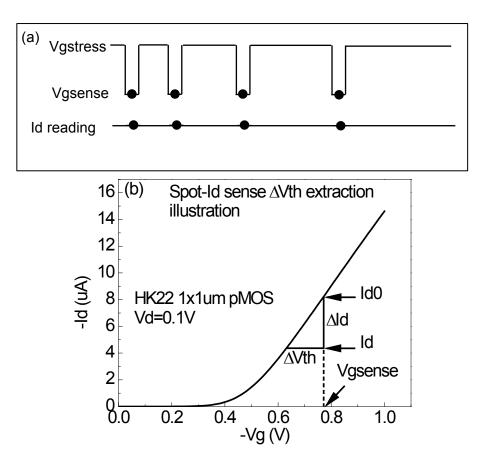

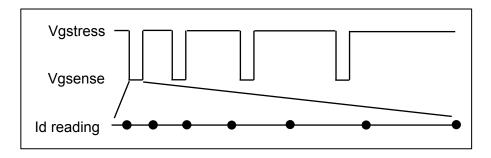

| F1g. | 2.3 Test waveform of Spot IV measurement. After each measurement $V_g$ firstly drops to zero and then rise to the next level to avoid potential stress during the measurement. Pulse units are adopted in spot-IV measurements so the measurement time for each point can be as low as (sub-) microseconds                                                                                                                                                                                                                                                                                 |

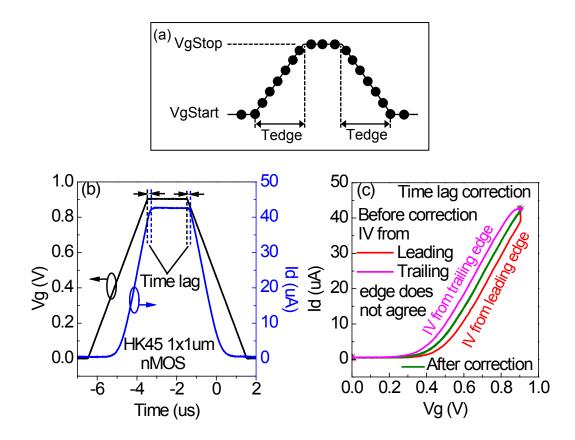

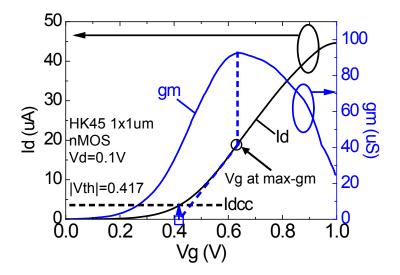

| Fig. | 2.4 (a) Typical waveform of a Pulse IV measurement. (b) Typical results of pulse IV. Dash lines are drawn at the switching point of both $V_g$ (black) and $I_d$ (blue), clearly $I_d$ measurement is lagging compared to $V_g$ measurement. This time lag results in a gap between the two IV curves measured from the leading and trailing edge of the $V_g$ pulse, as show in (c). This gap can be corrected by shift Id data forward against time to offset the time lag, as the green line shows in (c). 33                                                                           |

| Fig. | 2.5 Max- $g_m$ (blue dash lines) and constant current (black dash line) method extracted V <sub>th</sub> . Here I <sub>dcc</sub> is properly selected to intercept at the same V <sub>th</sub> as max- $g_m$ method on a fresh device                                                                                                                                                                                                                                                                                                                                                      |

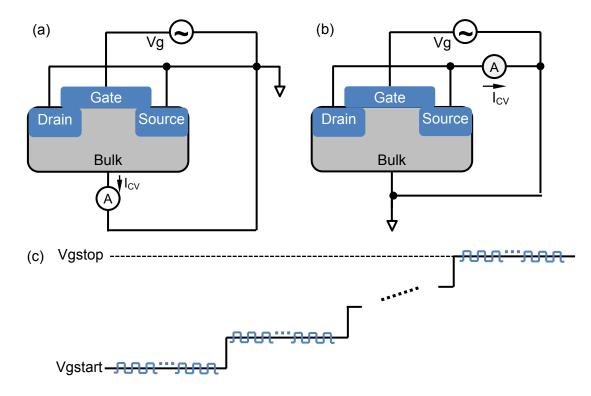

| Fig. | 2.6 Typical configuration and waveform for MOSFET split CV measurements.<br>(a) Drain and Source are both grounded to measure $C_{gb}$ , (b) Bulk is grounded,                                                                                                                                                                                                                                                                                                                                                                                                                             |

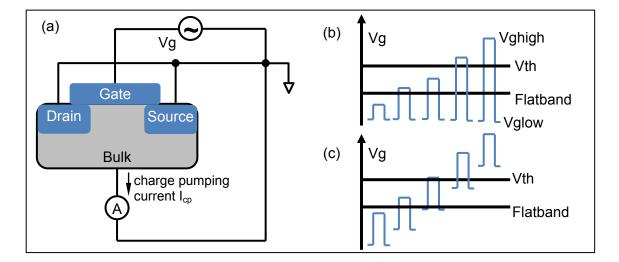

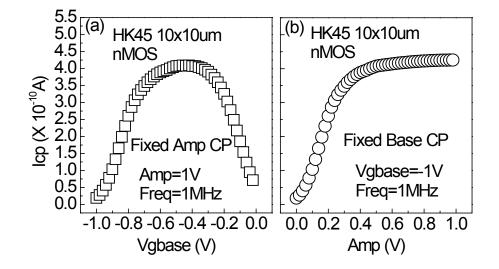

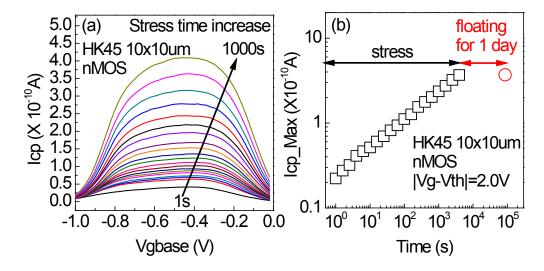

- Fig. 2.8 (a) Typical configuration of the charge pumping measurements on nMOSFET. (b) Fixed base charge pumping V<sub>g</sub> waveform. (c) Fixed Amplitude charge pumping V<sub>g</sub> waveform.

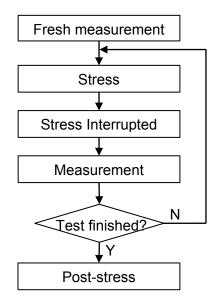

Fig. 2.10 Flow chart of a Measure-Stress-Measure (MSM) test scheme...... 42

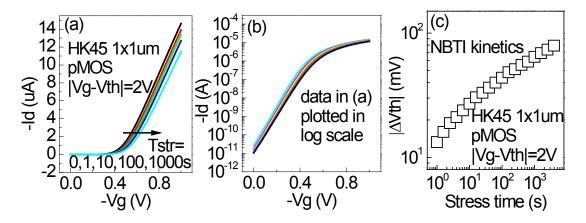

- Fig. 2.13. (a) Test waveform of Spot  $I_d$  sense MSM method. (b) Illustration of  $|\Delta V_{th}|$  extraction of Spot  $I_d$  sense MSM measurement. 45

- Fig. 2.14. The impact of different sensing techniques on the degradation. The increase of  $|\Delta V_{th}|$  will reduce the surface potential if the constant sensing  $V_g$  is used and thus leads to the lower degradation when compared with sensing at the constant current level which is approximately at the same surface potential. ... 46

- Fig. 2.16 Test waveform illustration of the extended Id sense measurement technique. The waveform is very similar to spot-I<sub>d</sub> MSM, except extended Id sense technique takes multiple measurements instead of one at the V<sub>gsense</sub> level....... 47

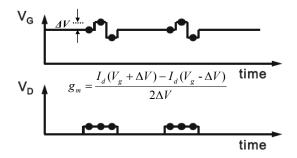

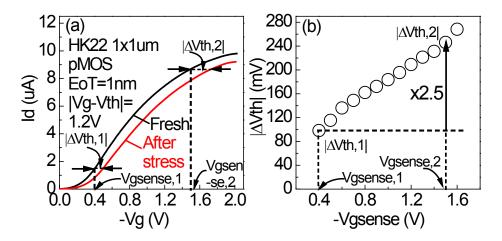

- Fig. 2.19 (a) Illustration of |ΔV<sub>th</sub>| extracted at different sensing V<sub>g</sub>. Pulse IV MSM is carried out on HK22 1x1um pMOSFET under |V<sub>g</sub>-V<sub>th</sub>|=1.2V 1ks NBTI stress.

(b) |ΔV<sub>th</sub>| against V<sub>gsense</sub> plot. |ΔV<sub>th</sub>| extracted from V<sub>gsense</sub>=1.5V is 2.5 times higher compared to V<sub>gsense</sub>=-0.4V.

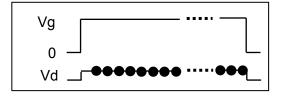

- Fig. 2.23. Test waveform of the Spot Id DMP technique...... 55

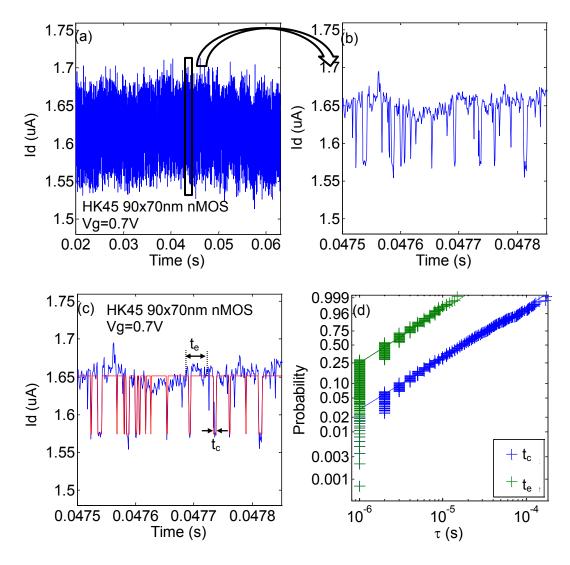

- Fig. 2.27 (a) RTN measured on a HK45 90x70nm nMOS.  $V_g$  is biased at  $V_g=V_{th}+0.2=0.7V$ , drain is biased at constant  $V_d=+100mV$ , sampling

|       | rate=1MSa/s to capture the fast RTN signal. (b) Enlarge the data marked in                                                                                         |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | black rectangle from (a) to show a clear RTN is observed. (c) RTN information:                                                                                     |

|       | Amplitude, $t_c$ and $t_e$ extraction. (d) $t_c$ and $t_e$ follow a good exponential                                                                               |

|       | distribution                                                                                                                                                       |

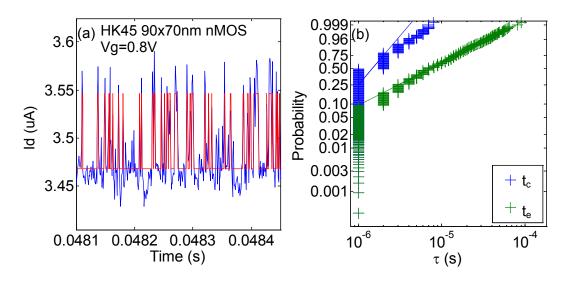

| Fig.  | 2.28 (a) RTN measurement and analysis on the same device under $V_g=0.8V$ ,                                                                                        |

| 0     | clearly $t_c$ decrease and $t_e$ increases under a higher $V_g$ compared to Fig. 2.27c. (b)                                                                        |

|       | $\tau_c$ and $\tau_e$ under 0.8V also follow a good exponential distribution                                                                                       |

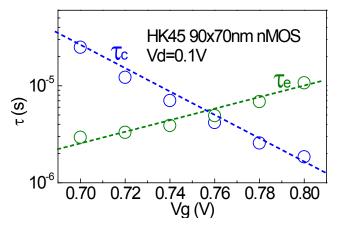

| Fig   | 2.29 RTN $\tau_c$ and $\tau_e$ dependence on V <sub>g</sub> . Trap energy information can be extracted                                                             |

| 1 ig. | $2.23$ KTTV $c_c$ and $c_s$ dependence on $v_g$ . Trap energy information can be extracted from this                                                               |

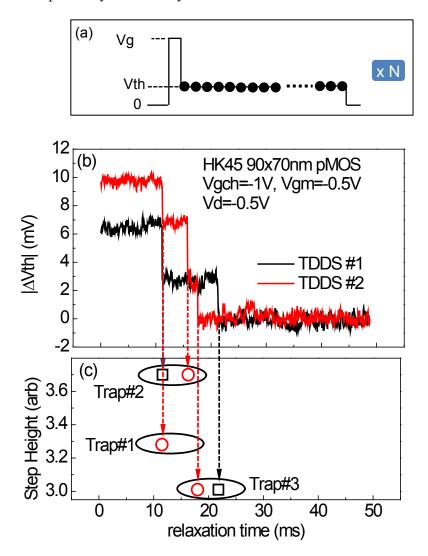

| Fig   | 2.30 (a) Test waveform of the Time Dependent Defect Spectroscopy (TDDS)                                                                                            |

| гıg.  |                                                                                                                                                                    |

|       | technique. (b) Typical TDDS measurement results, each step represents a single                                                                                     |

|       | defect emission, the amplitude and emission time of this defect is then extracted.                                                                                 |

|       | (c) By repeating the TDDS measurements a defect spectroscopy in terms of                                                                                           |

|       | emission time and amplitude can be extracted                                                                                                                       |

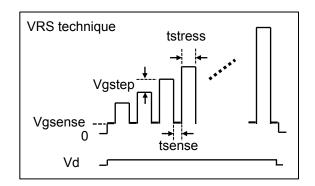

| -     | 2.31 Test waveform of the Voltage Ramp Stress (VRS) technique                                                                                                      |

| Fig.  | 2.32 A replot of the Voltage Ramp Stress technique results and analysis in [88]                                                                                    |

|       | to show parameter extraction from the Voltage Ramp Stress technique. PBTI on                                                                                       |

|       | nMOSFETs is adopted here. a-c show the test data and A,m,n extraction using                                                                                        |

|       | conventional Constant Voltage Stress technique, d-f show the test data and                                                                                         |

|       | parameter extraction of Voltage Ramp Stress technique. The agreement of                                                                                            |

|       | parameters extracted from these two different techniques indicates the                                                                                             |

|       | correctness of the Voltage Ramp Stress technique                                                                                                                   |

| Fig.  | 2.33 Voltage Step Stress test waveform illustration                                                                                                                |

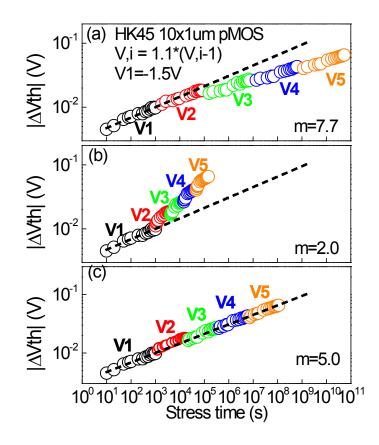

|       | 2.34 Typical results of applying the Voltage Step Stress technique on a HK45                                                                                       |

| U     | 1x1um pMOSFET. Firstly BTI kinetics under $V_g=V_1$ is used to extract A & n,                                                                                      |

|       | the rest data under high $V_g$ is then used to extract m                                                                                                           |

| Fig   | 2.35 Stress time transformation with different voltage exponent, m. Only when                                                                                      |

| 0     | the correct m is used, they agree well with the power law predetermined in the                                                                                     |

|       | first step (dashed line)                                                                                                                                           |

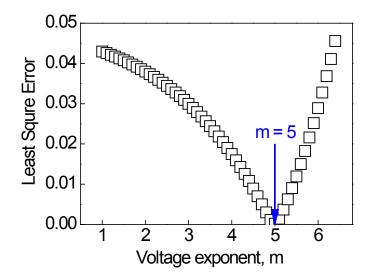

| Fio   | 2.36 Least Square Error between the transformed curve (the points in Fig. 2.35)                                                                                    |

| 1 19. | and the dashed line extrapolated from the first step (dash line in Fig. 2.35) 68                                                                                   |

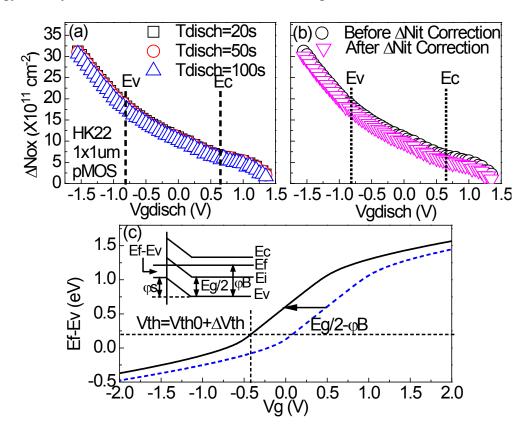

| Fig   | 3.1 (a) A comparison of the energy profiles before and after stress, $ \Delta V_{th} $ impact                                                                      |

| 1 15. | on energy level $E_f - E_v$ has already been taken into consideration. (b) By                                                                                      |

|       |                                                                                                                                                                    |

|       | subtracting the fresh profile from the stressed one, the profile of Generated                                                                                      |

|       | Defects was extracted. (c) Illustration of the energy range for the Cyclic Positive<br>Changes (CPC) and the Anti Neutralization Desitive Changes (ANDC). Note the |

|       | Charges (CPC) and the Anti-Neutralization Positive Charges (ANPC). Note the                                                                                        |

|       | illustration is just a "rule-of-thumb" here for convenience, Ec and Ev is not the                                                                                  |

|       | precise boundary to separate CPC and ANPC from energy location point of                                                                                            |

|       | view                                                                                                                                                               |

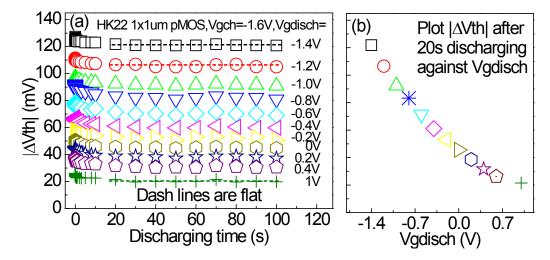

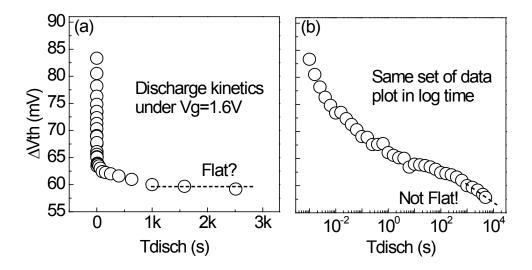

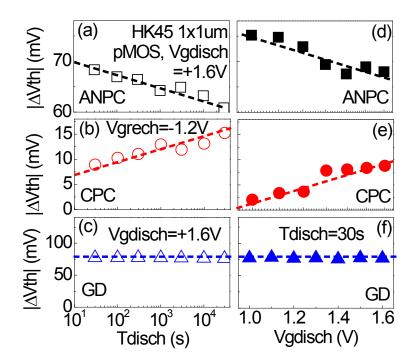

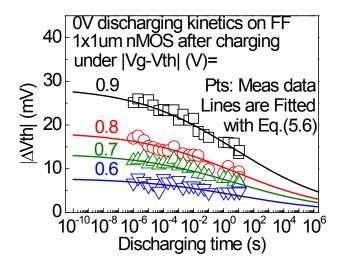

- Fig. 3.2 Discharging kinetics under positive gate voltage in (a) linear time scale and (b) log time scale. Clearly the discharging won't become flat although it looks so in linear time plot in (a).73

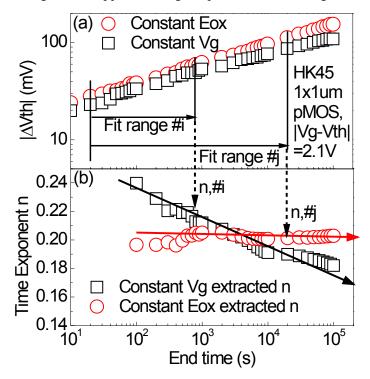

- Fig. 3.13 (a) Kinetics of Generated Defects measured under constant  $V_g$  and  $E_{ox}$  NBTI stress. (b) The extracted time exponent n using data between 10s and variable end-time. n varies little after  $10^3$ s for constant Eox stress, in which the

|       | overdrive $ V_{gstress}-V_{th} $ is kept constant during the test. If the test is carried out under constant $V_g$ stress, a gradual reduction can be observed |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

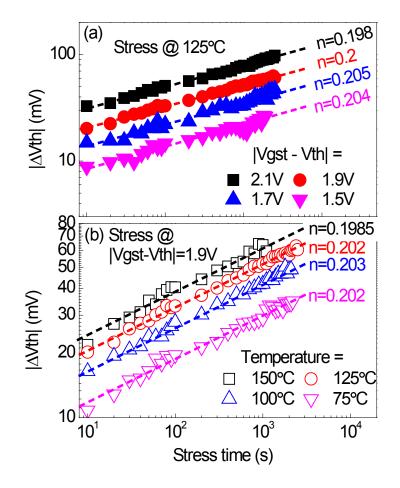

| Fig.  | 3.14 Kinetics of Generated Defects under different (a) stress voltages and (b) temperatures. The time exponents equal to 0.2 for all circumstances             |

| Fig.  | 3.15 Verification of Generated Defects calculated with Equation (3.2). Note the test data is not used for parameter extraction                                 |

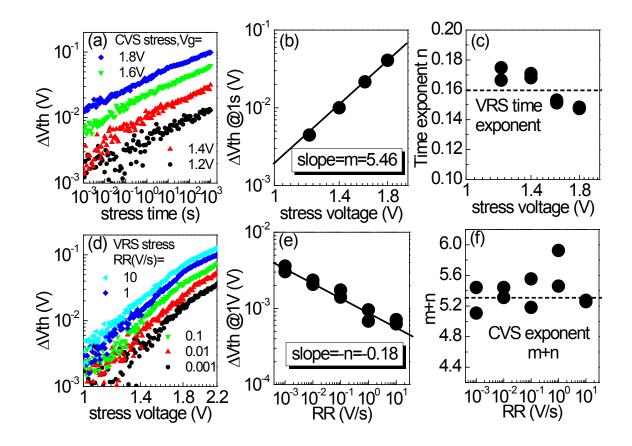

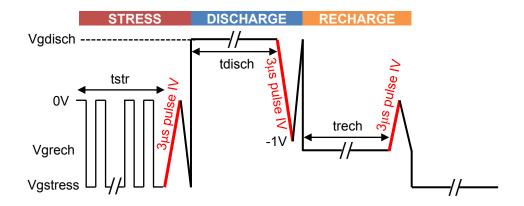

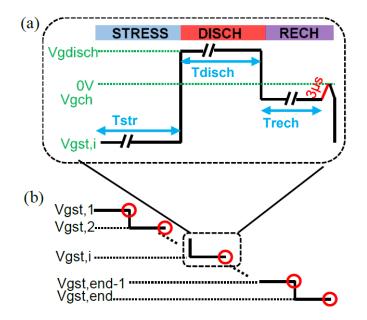

| Fio   | 3.16 Test waveform of the AC Stress-Discharge-Recharge technique                                                                                               |

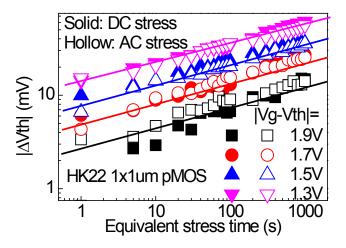

|       | 3.17 Generated Defects measured under DC and AC Stress-Discharge-Recharge                                                                                      |

| 1 18. | method agrees very well. Equivalent stress time for AC is calculated by stress time*duty factor                                                                |

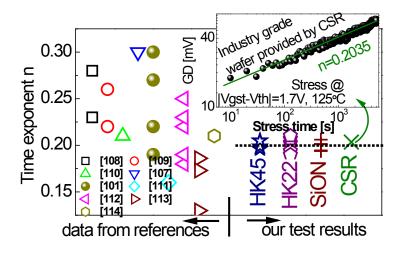

| Fig   | 3.18 A comparison of NBTI time exponent reported by early works [107-114]                                                                                      |

| 1 15. | with Generated Defects' time exponent values extracted using the SDR method.                                                                                   |

|       | Multiple points for each process represent the values from different stress                                                                                    |

|       | voltage and temperature. The inset shows results on the CSR sample                                                                                             |

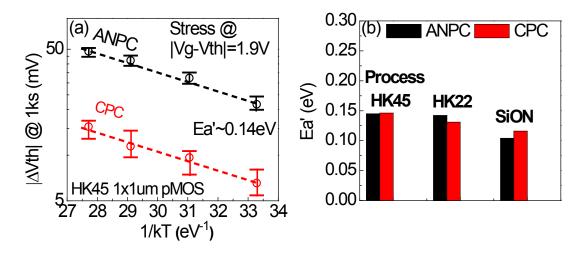

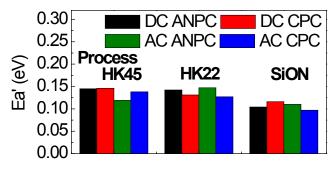

| Fig.  | 3.19 Å summary of the activation energy Ea' of ANPC and CPC under DC/AC                                                                                        |

| -     | NBTI stress condition on 3 different processes                                                                                                                 |

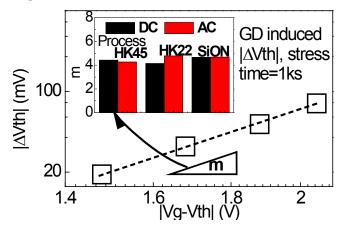

| Fig.  | 3.20 $ V_g-V_{th} $ exponent m extraction. The data points (' $\Box$ ') is taken from Fig.                                                                     |

|       | 3.14a. The inset shows the extracted m value for DC and AC stress conditions                                                                                   |

|       | across 3 different processes                                                                                                                                   |

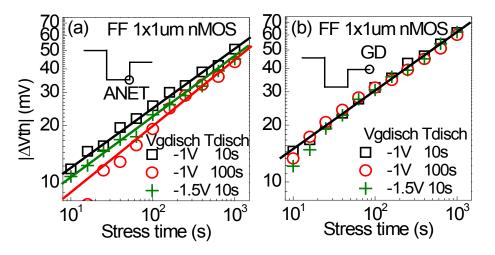

| Fig.  | 3.21 Typical results of Stress-Discharge-Recharge technique on nMOSFETs.                                                                                       |

|       | The degradation is monitored by measuring pulse IV in 3us. It is clearly shown                                                                                 |

|       | that Anti-Neutralization Electron Traps (ANET) vary with different $ V_{gdisch} $ and                                                                          |

|       | T <sub>disch</sub> (a) while the entire Generated Defects are independent of measurement condition (b)                                                         |

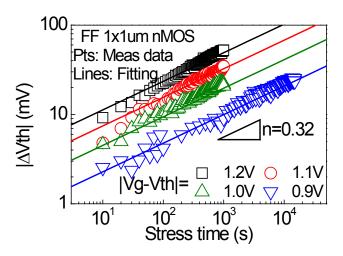

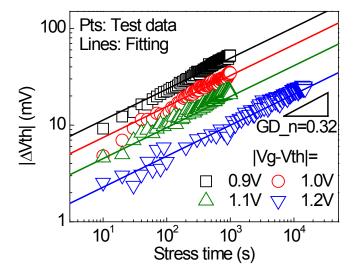

| Fig   | 3.22 Generated Defects under different $ V_g-V_{th} $ PBTI stress also follow a power                                                                          |

| 1 15. | law but with a larger much time exponent $n=0.32$ . Tests are following the                                                                                    |

|       | Stress-Discharge-Recharge procedure, $V_{gdisch}$ =-1V, $V_{grech}$ =0.5V                                                                                      |

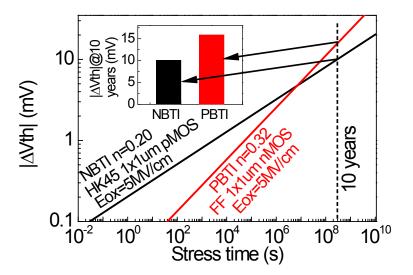

| Fig.  | 3.23 Comparison of the kinetics of Generated Defects under oxide electric field                                                                                |

| U     | $E_{ox}$ =5MV/cm, T=125°C N/PBTI stress. The inset compares Generated Defects                                                                                  |

|       | under N/PBTI after 10 years                                                                                                                                    |

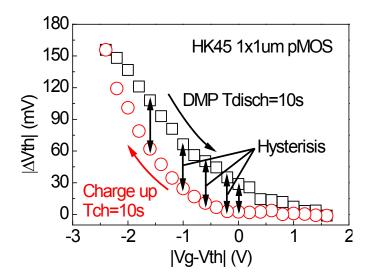

| Fig.  | 4.1 Pre_Existing defects' profile extraction from charge up and DMP pattern. A                                                                                 |

|       | big hysteresis is observed                                                                                                                                     |

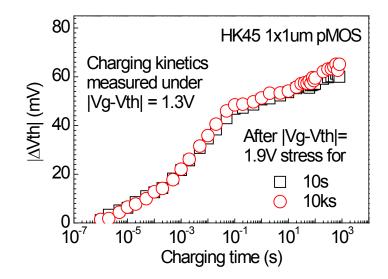

| Fig.  | 4.2 Charging kinetics under the same $ V_g-V_{th} =1.3V$ after stressing under $ V_g-V_{th} =1.3V$                                                             |

|       | $V_{th}$ =1.9V for 10s and 10ks. Stressed Vth is used as reference so both kinetics                                                                            |

|       | starts from 0. The perfect agreement indicates the charging here is purely the                                                                                 |

| ъ.    | filling of Pre_Existing defects, which is independent of stress time                                                                                           |

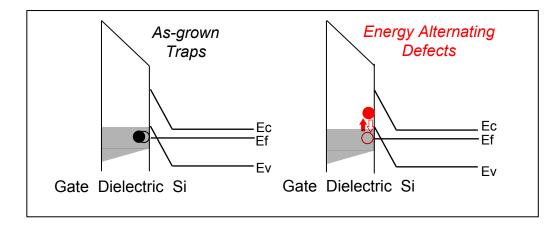

| Fig.  | 4.3 Illustration of two components in Pre_Existing defects: As-grown Traps and                                                                                 |

|       | Energy Alternating Defects. Charged As-grown Traps will be discharged once                                                                                     |

|       | $ V_g $ lowers down, while charged Energy Alternating Defects cannot be discharged as its energy is alternating. For details about the DMP principle refer     |

|       | to section 2.5                                                                                                                                                 |

|       | 100 Section 2.5                                                                                                                                                |

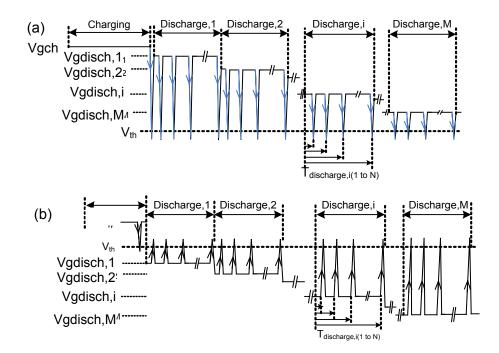

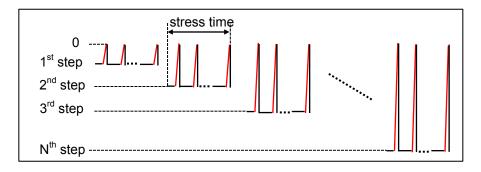

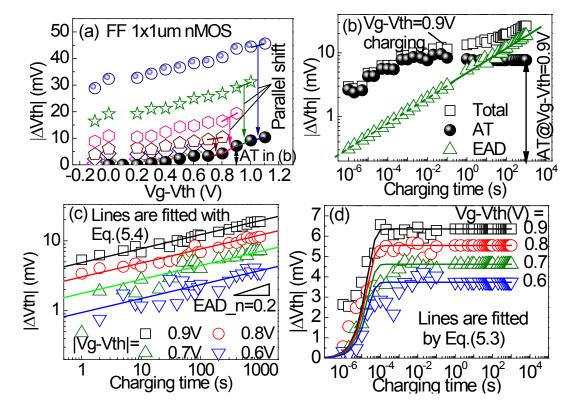

| <ul> <li>Fig. 4.4 (a) Illustration of the m-DMP test waveform. (b) Illustration of As-grown Traps' profile extraction using the m-DMP technique</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AT in (a) from the total Pre_Existing trap over 1s charging kinetics ('\[]'). AT kinetics ('\[]') is then obtained by subtracting Energy Alternating Defects' power law kinetics (dashed line) from total ('\[]')                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <ul> <li>Fig. 4.6 Energy Alternating Defects' charging follows a power law (a) with a  V<sub>g</sub>-V<sub>th</sub>  independent time exponent (b). EAD also follows power law against  V<sub>g</sub>-V<sub>th</sub>  (c).</li> <li>102</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

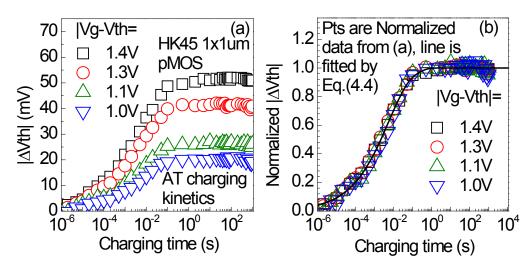

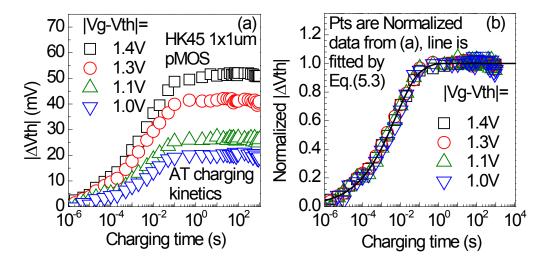

| Fig. 4.7 As-grown Traps' charging under different $ V_g-V_{th} $ (a). (b) By normalizing against the saturated level at each $ V_g-V_{th} $ , the kinetics overlaps each other and follows stretched exponent kinetics as described by Equation (4.4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Fig. 4.8 As-grown Traps' profile extracted using m-DMP technique under different temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

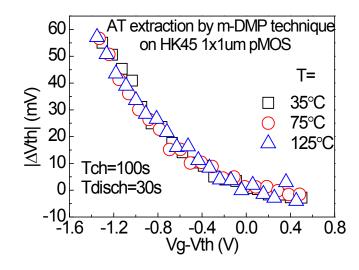

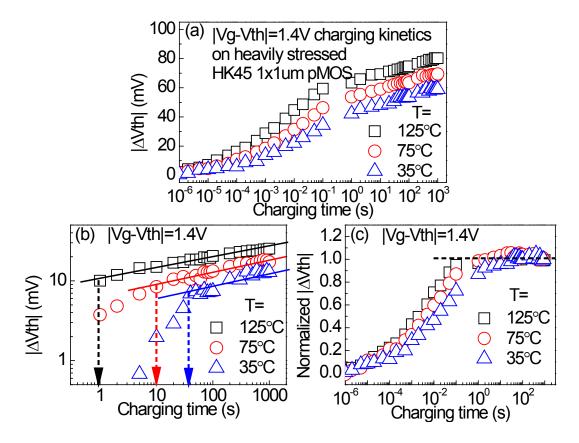

| <ul> <li>Fig. 4.9 (a) Pre_Existing defects' charging kinetics at the same  V<sub>g</sub>-V<sub>th</sub>  under different temperatures. (b) Energy Alternating Defect (EAD) charging kinetics under different temperature, calculated by subtracting the same amount of saturated As-grown Traps (AT) from Pre_Existing defects' charging kinetics in (a). Note under 75°C and 35 °C, AT charging is much slower compared to 125°C thus 1s is not long enough for AT charging to reach saturation. EAD power law parameters should be extracted from a much higher starting stress time under low temperatures, as shown in the dashed arrows. (c) Normalized AT charging kinetics after subtracting the extrapolated EAD kinetics fitted with the solid lines in (b).</li> </ul> |

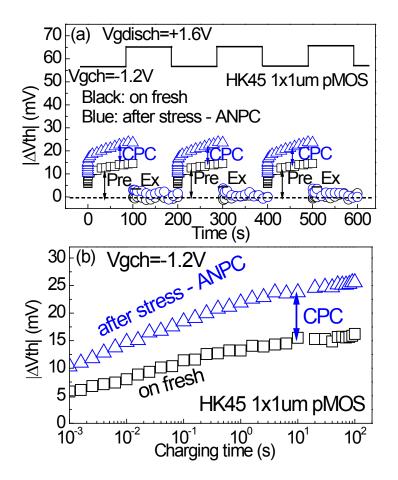

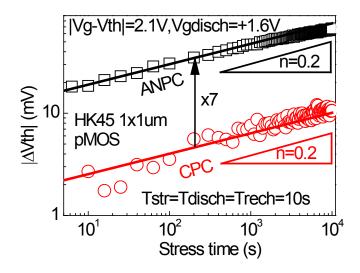

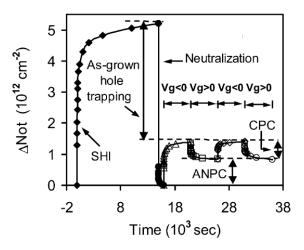

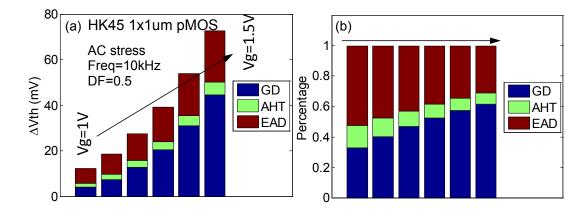

| Fig. 5.1 First paper clearly separates hole trap generation into 2 parts: Cyclic Positive Charges (CPC) & Anti-Neutralization Positive Charges (ANPC) [124] 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

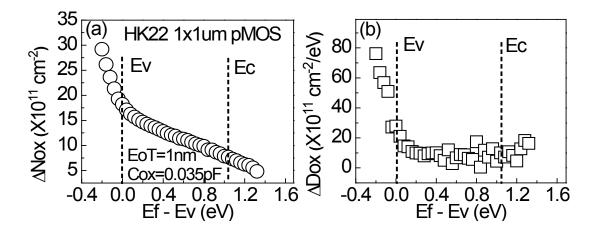

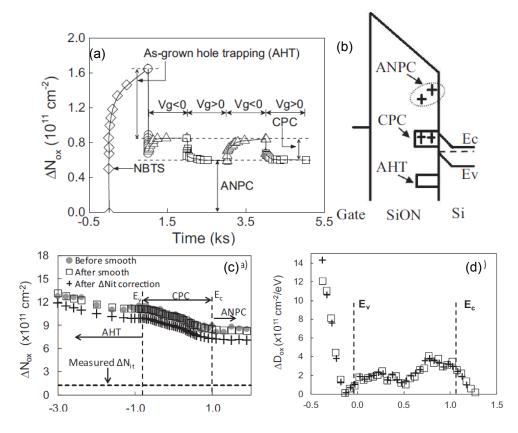

| Fig. 5.2 Illustration of energy location of As-grown Hole Traps (AHT), Cyclic<br>Positive Charges (CPC) & Anti-Neutralization Positive Charges (ANPC) (a&b),<br>based on the defect profile results (c&d) measured with Discharging-based<br>Multiple Pulses (DMP) technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Fig. 5.3 Illustration of the A-G model proposed by Z. Ji et al [78]. (a) Independent<br>As-grown Hole Traps' profile of stress time. (b). $ \Delta V_{th} $ consists of a fast<br>saturated As-grown Hole Traps component plus Generated Defects , which<br>follow a power law                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Fig. 5.4 Illustration of the A-G model based on the understanding and separation of different type of defects. 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <ul> <li>Fig. 5.5 (a) Kinetics of Generated Defects under different  V<sub>g</sub>-V<sub>th</sub>  stress condition.</li> <li>(b) Generated Defects' time exponent n is independent from  V<sub>g</sub>-V<sub>th</sub> . (c).  V<sub>g</sub>-V<sub>th</sub>  exponent extraction.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Fig. | 5.6 As-grown Traps' charging under different $ V_g-V_{th} $ (a). (b) By normalizing         |

|------|---------------------------------------------------------------------------------------------|

|      | against the saturated AT under different $ V_g\text{-}V_{th} $ , the kinetics overlaps each |

|      | other and follows stretched exponent kinetics in Equation (5.3) 114                         |

| Fig. | 5.7 (a) Energy Alternating Defects charging kinetics under different  Vg-Vth  on a          |

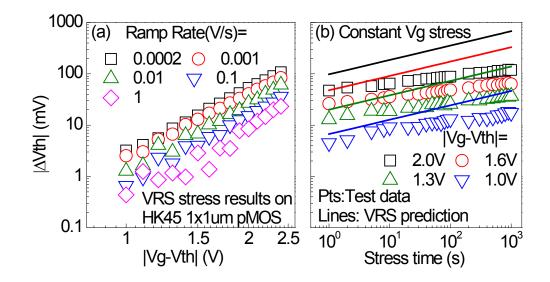

- Fig. 5.8 (a) Typical results of applying Voltage Ramp Stress technique on HK45 pMOSFET. (b) Comparison of the test data measured under conventional Constant Voltage Stress with the Voltage Ramp Stress technique predicted value. 116

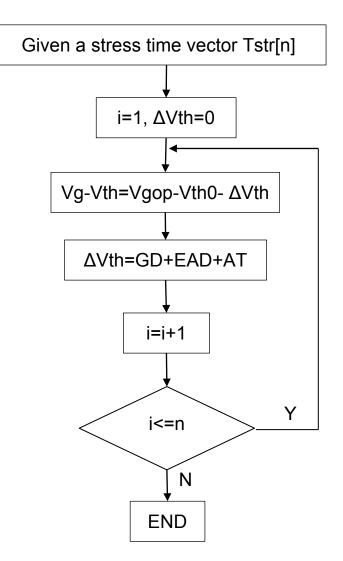

- Fig. 5.13 Procedure to calculate  $|\Delta V_{th}|$  under constant voltage stress with parameters extracted under constant  $|V_g-V_{th}|$ . 121

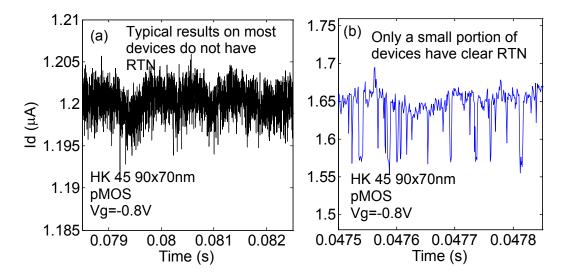

| Fig. 6. | 1 Most nano- | -scale devices s | show a sto | chastic of | current f | luctuation ( | a) instead | of a |

|---------|--------------|------------------|------------|------------|-----------|--------------|------------|------|

| cl      | ear RTN (b)  | . Sampling rate  | e = 1MSa/s | s is used  | here      |              |            | 136  |

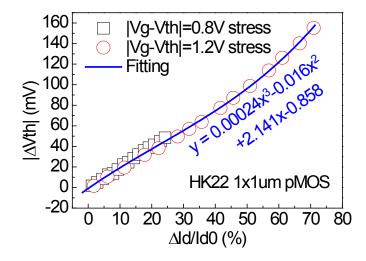

- Fig. 6.4  $|\Delta V_{th}| \sim \Delta I_d/I_{d0}$  relationship extracted from the charging kinetics on a HK45 90x70nm pMOS under different  $|V_g-V_{th}|$ . Note the conversion is device specified. 141

- Fig. 6.8 (a) Multiple WDF<sup>+</sup> measurements and their averaged value under AC NBTI.

(b) Averaged WDF<sup>+</sup> overlaps for DC and AC of different frequency and duty factor.

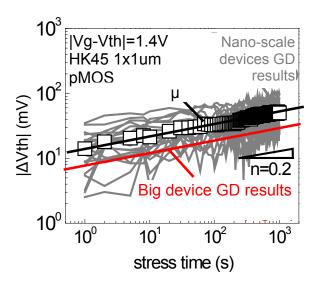

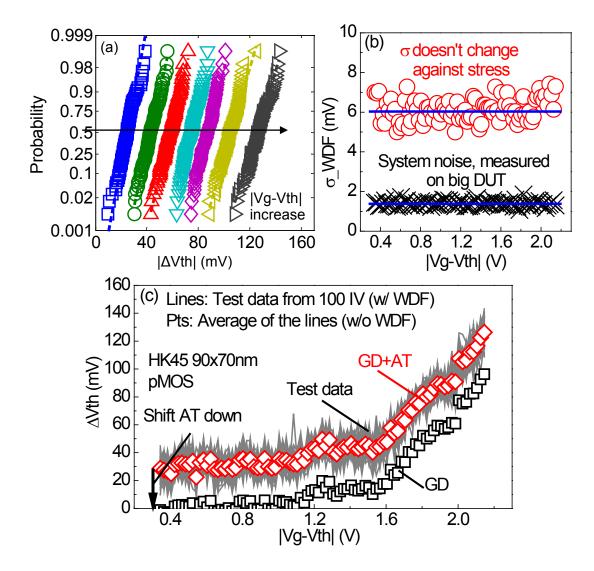

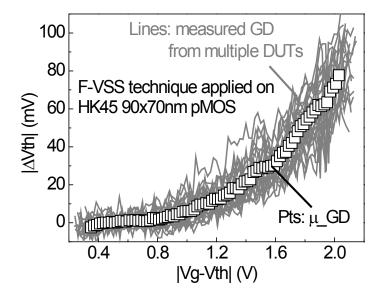

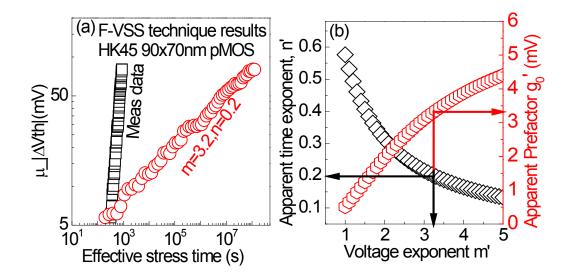

- Fig. 6.11 Typical results of Generated Defects (GD) measured on a **SINGLE** nanoscale device. (a) Statistical Within-Device-Fluctuation distrbiution of  $|\Delta V_{th}|$ from 100 IV curves measured after each  $|V_g-V_{th}|$  step. (b) The standard deviation for the data in (a) ('o') and the data from large device ('x').  $\sigma_WDF$  from nanoscaled device is much larger than the one from large device which is dominated by system noise. In addition,  $\sigma_WDF$  changes little with stress  $|V_g-V_{th}|$ , confirming that it is dominated by As-grown Traps (AT). (c) For each  $|V_g-V_{th}|$ ,

the 100  $|\Delta V_{th}|$  were ploted as lines and their mean value as ' $\diamond$ '. Generated Defects (' $\Box$ ') were obtained by subtracting As-grown Traps in the flat plateau. 149

- Fig. 6.16 (a) A replot of Fig. 6.12. Generated Defects results of Fast-Voltage Step Stress technique. (b) Plot  $\sigma \sim \mu$  from (a) to extract  $\eta$  of Generated Defects. ..... 155

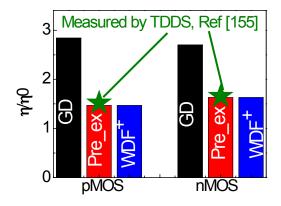

- Fig. 6.18 Trap impact,  $\eta/\eta_0$ , for Generated Defects, Pre\_Existing defects and WDF<sup>+</sup> for pMOS and nMOS.  $\eta_0$  is the impact of a single charge in the charge sheet approximation calculated by  $\eta_0=q/C_{OX}$ , where q is the elementary charge and Cox the gate oxide capacitance in inversion.  $\eta/\eta_0$  extracted using Time Dependent Defect Spectroscopy (TDDS) [29] is also plotted for comparison. 156

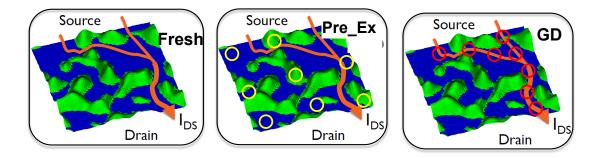

- Fig. 6.19 Illustration of a potential explanation for the larger average impact of a single defect ( $\eta$ ) of Generated Defects compared with Pre\_Existing defects. Generated Defects are more likely located above the current percolation path due to channel-carrier assisting defect generation, resulting in a higher  $\eta$  compared with the random distributed Pre Existing defects. 156

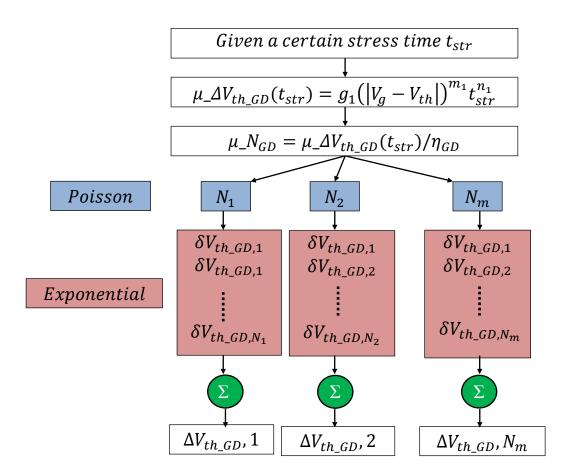

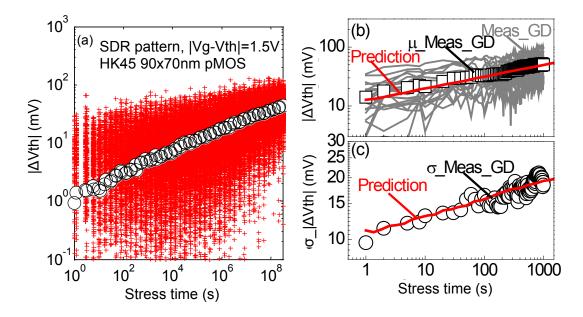

| Fig. | 6.21 (a) Simulated kinetics of Generated Defects (GD) under $ V_g-V_{th} =1.5V$                  |

|------|--------------------------------------------------------------------------------------------------|

|      | NBTI. Each '+' represents one simulated device. The 'o' at each stress time is                   |

|      | the average of 3000 devices. Good agreement is achieved between the test data                    |

|      | and simulaton of (b) $\mu_{\Delta}V_{th_{GD}}$ and (c) $\sigma_{\Delta}V_{th_{GD}}$              |

| Fig. | 6.22 Probability plot of data in Fig. 6.21a. The distribution of the test data                   |

|      | (symbols) can be well predicted by the simulation results (lines)                                |

| Fig. | 6.23 Procedure to simulate Time Dependent Variability on nano-scale devices                      |

| -    | based on the A-G framework. "Defect Centric statistics" represent the entire                     |

|      | procedure in Fig. 6.20                                                                           |

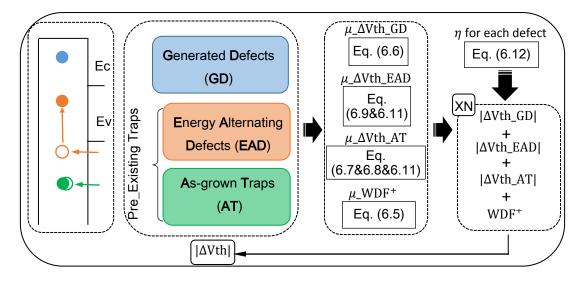

| Fig. | 6.24 Illustration of the comprehensive A-G framework based on the A-G model                      |

| _    | and defect centric theory                                                                        |

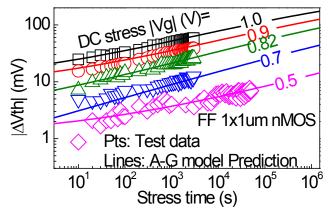

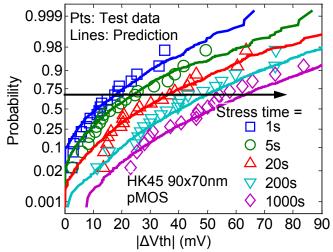

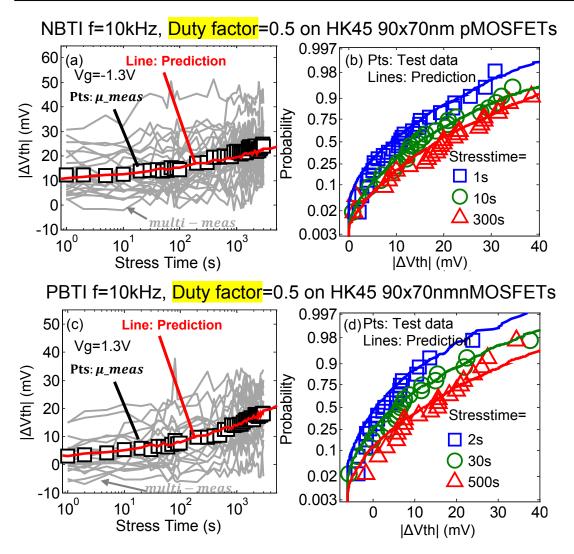

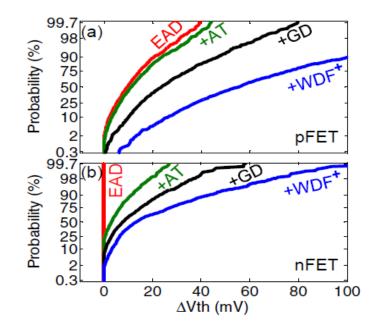

| Fig. | 6.25 Demonstration of the A-G frameowrk's predicting capability on HK45                          |

| _    | 90x70nm devices under AC NBTI (a&b) and PBTI (c&d) stress. a&c compare                           |

|      | the averaged value ('□')from multiple device measurements (grey lines) and the                   |

|      | prediction from 1000 Monto-Carlo simulation with the A-G framework                               |

|      | considering both Time-zero Variability and Time Dependent Variability. b&d                       |

|      | compares the distributions at different stress time                                              |

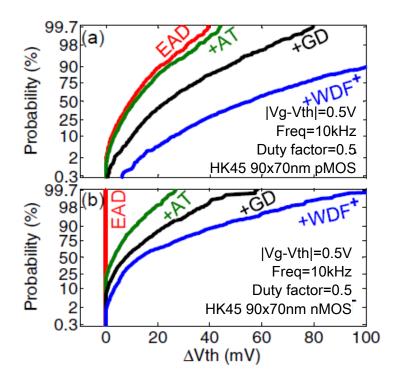

| Fig. | 6.26 10-year degradation under AC NBTI (a) and PBTI (b) with contribution                        |

|      | from different type of defects. $ V_g-V_{th} =0.5V$ , Freq=10kHz, Duty factor=0.5.               |

|      | 1000 Monto-Carlo simulations were performed                                                      |

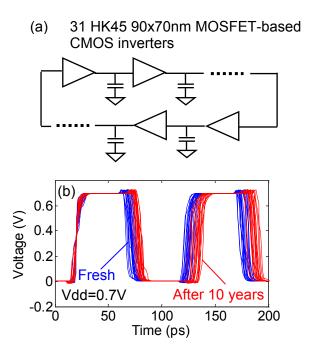

| Fig. | 6.27 (a) A typical 31-stage Ring Oscillator (RO) circuit used for the HSPICE                     |

|      | circuit simulation. (b) Snapshot of the waveform from one node of the RO                         |

|      | before and after 10 years under the operating voltage $V_{dd}$ =0.7V. 1000 run                   |

|      | Monto-Carlo simulation is used 165                                                               |

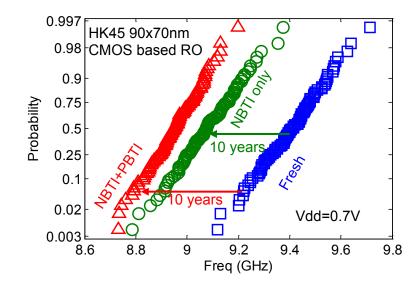

| Fig. | 6.28 Probablity plot of the RO frequency before and after 10 years. The                          |

|      | simulation with taking only NBTI into consideration is also compared with the                    |

|      | simulation with both NBTI and PBTI. The difference reveals that PBTI should                      |

|      | not be neglected                                                                                 |

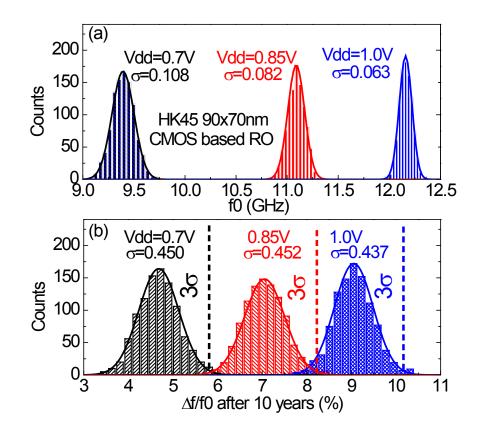

| Fig. | 6.29 Simulation results of 1000 ROs based on HK45 90x70nm CMOS. (a)                              |

|      | Distribution of the fresh RO frequency ( $f_0$ ) under different V <sub>dd</sub> . By increasing |

|      | $V_{dd},\ RO$ performance increases (higher $f_0)$ and the impact of Time-zero                   |

|      | Variability becomes smaller (decreasing $\sigma$ ). (b) The RO frequency degradation             |

|      | $(\Delta f/f_0)$ after 10 years is increasing with higher V <sub>dd</sub>                        |

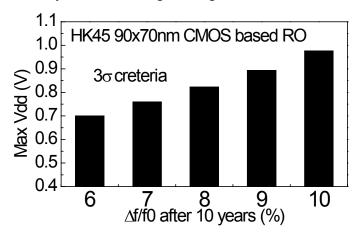

| Fig. | 6.30 Max $V_{dd}$ predicted by the A-G framework based RO simulation with                        |

|      | different failure criteria ( $\Delta f/f_0$ from 6% to 10%)                                      |

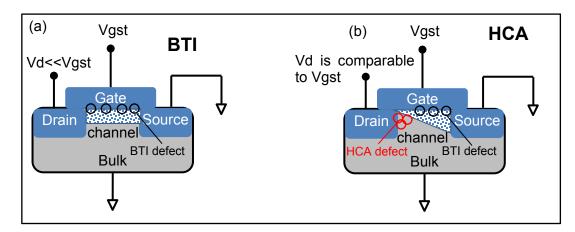

| Fig. | 7.1 Illustration of the MOSFET voltages under (a) BTI stress and (b) Hot Carrier                 |

|      | Aging (HCA) stress                                                                               |

| Fig. | 7.2 A replot of Fig. 6.26. 10-year degradation under AC NBTI (a) and PBTI (b)                    |

|      | with contribution from different types of defects. $ V_g-V_{th} =0.5V$ , Freq=10kHz,             |

|      | Duty factor=0.5. 1000 Monto-Carlo simulations were performed 175                                 |

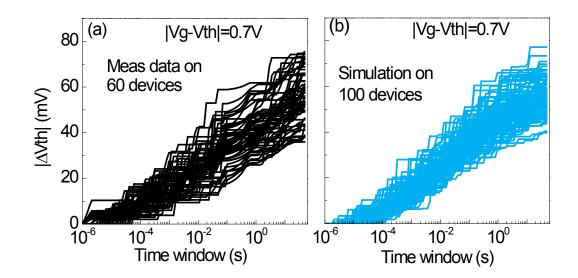

| Fig. | 7.3 | Measured    | WDF    | data  | on  | 60   | devices | (a) | can | be | well | reproduced | by | 100 |

|------|-----|-------------|--------|-------|-----|------|---------|-----|-----|----|------|------------|----|-----|

|      | Mo  | nte-Carlo V | VDF si | mulat | ion | (b). |         |     |     |    |      |            |    | 176 |

### **List of Tables**

| Table 1.1 Explanation of parameters used in the R-D Model                                                                                      |                         |

|------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Table 1.2 Cumulative Distribution Function (CDF) in a standard normal dis                                                                      | stribution              |

|                                                                                                                                                |                         |

| Table 1.3 Impact of a single trap as the scaling down of MOSFET size [49]                                                                      |                         |

| Table 2.1 Test sample information                                                                                                              |                         |

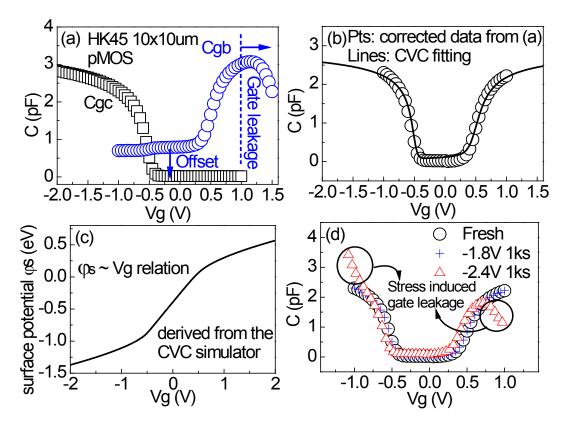

| Table 2.2 MOSFET parameters extracted from fitting the measured CV                                                                             | with the                |

| CVC simulator                                                                                                                                  |                         |

| Table 5.1 The A-G model parameters extracted on HK45 1x1um pMOS und                                                                            | ler NBTI                |

| stress                                                                                                                                         | 125                     |

| Table 5.2. The A-G model parameters under PBTI stress                                                                                          | 131                     |

| Table 6.1 Extracted parameters of the A-G framework under NBTI/PBTI                                                                            | stress on               |

| HK45 90x70nm pMOSFET/nMOSFETs. All the $ \Delta V_{th} $ related param                                                                         | eters (g <sub>1</sub> , |

| g <sub>2</sub> , p <sub>1</sub> , p <sub>3</sub> , $\eta_{GD}$ , $\eta_{Pre\_Ex}$ , $\eta_{WDF+}$ ) are in millivolts and timing related param | neters (τ,              |

| t <sub>0</sub> ) are in seconds.                                                                                                               | 162                     |

## **Table of Contents**

| A | cknowled                                               | lgements                                                        | i   |

|---|--------------------------------------------------------|-----------------------------------------------------------------|-----|

| A | bstract                                                |                                                                 | ii  |

| L | ist of Abl                                             | previations                                                     | iv  |

| L | ist of Syn                                             | nbols                                                           | v   |

| L | ist of Fig                                             | ures                                                            | vi  |

| L | ist of Tab                                             | les                                                             | XX  |

| T | able of C                                              | ontents                                                         | xxi |

| 1 | Introdu                                                | ction of Bias Temperature Instability (BTI) Lifetime Prediction | 1   |

|   | 1.1 A r                                                | eview of BTI lifetime prediction                                | 1   |

|   | 1.1.1                                                  | Introduction of BTI                                             | 2   |

|   | 1.1.2                                                  | Origin of BTI                                                   | 4   |

|   | 1.1.3                                                  | Accelerate characterization of BTI                              | 6   |

|   | 1.1.4                                                  | BTI Recovery                                                    | 8   |

|   | 1.2 A review of Bias Temperature Instability modelling |                                                                 |     |

|   | 1.2.1                                                  | Reaction-Diffusion (R-D) model                                  | 9   |

|   | 1.2.2                                                  | Two-Stage Model                                                 | 16  |

|   | 1.2.3                                                  | As-grown Generation (A-G) Model                                 | 19  |

|   | 1.3 Cha                                                | allenges in predicting BTI lifetime on nano-scale devices       | 20  |

|   | 1.3.1                                                  | Device-to-Device Variability                                    | 20  |

|   | 1.3.2                                                  | Within Device Fluctuation                                       | 23  |

|   | 1.4 Def                                                | fect centric theory                                             | 24  |

|   | 1.5 Org                                                | ganization of this thesis                                       |     |

| 2 | Charact                                                | erization methodology                                           |     |

|   | 2.1 Intr                                               | oduction                                                        |     |

|   | 2.2 San                                                | nple preparation in this work                                   | 29  |

|   | 2.3 Typ                                                | pical electric characterization method                          |     |

|   | 2.3.1                                                  | I <sub>d</sub> -V <sub>g</sub> (IV) measurement                 |     |

|   | 2.3.2                                                  | Split Capacitance Voltage (CV) measurement                      | 35  |

|   | 2.3.3                                                  | Charge pumping measurement                                      |     |

|   | 2.4 Typ                                                | pical BTI Characterization scheme                               | 41  |

|   | 2.4.1                                                  | Measure-Stress-Measure (MSM) characterization method            | 41  |

|   | 2.4.2                                                  | On-the-Fly (OTF) characterization method                        | 49  |

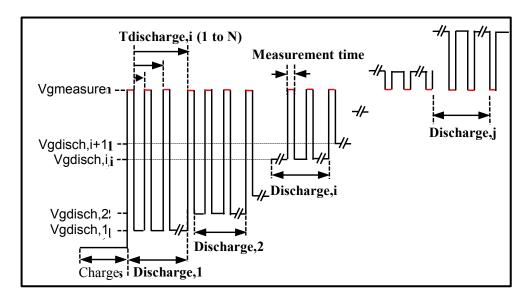

|   | 2.5 Dis                                                | charging-based Multiple Pulse (DMP) technique                   | 51  |

|   | 2.5.1                                                  | Conventional DMP technique                                      | 51  |

|   | 2.5.2                                                  | Spot Id DMP technique                                           | 53  |

|   | 2.6 Var                                                | riability characterization method                               | 57  |

|   | 2.6.1 Random Telegraph Noise (RTN) technique                                 | 57       |

|---|------------------------------------------------------------------------------|----------|

|   | 2.6.2 Time Dependent Defect Spectroscopy (TDDS) technique                    | 60       |

|   | 2.7 Accelerated BTI parameter extraction technique                           | 61       |

|   | 2.7.1 Voltage Ramp Stress technique                                          | 62       |

|   | 2.7.2 Voltage Step Stress technique                                          | 65       |

|   | 2.8 Summary                                                                  | 68       |

| 3 | Defect Generation under BTI stress                                           | 70       |

|   | 3.1 Introduction & Motivation                                                | 70       |

|   | 3.2 Generated Defects under NBTI stress                                      | 71       |

|   | 3.2.1 Energy profile of Generated Defects: Cyclic Positive Charges (CPC) and | nd Anti- |

|   | Neutralization Positive Charges (ANPC)                                       | 71       |

|   | 3.2.2 Characterization method of CPC and ANPC                                | 73       |

|   | 3.2.3 Speculation of the origin of CPC and ANPC                              | 77       |

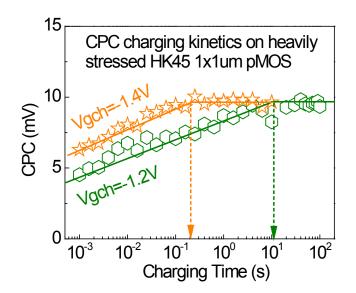

|   | 3.3 ANPC and CPC generation kinetics                                         | 77       |

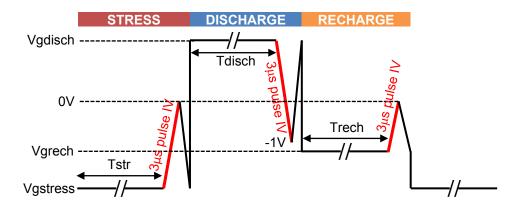

|   | 3.3.1 Novel Stress-Discharge-Recharge technique                              | 77       |

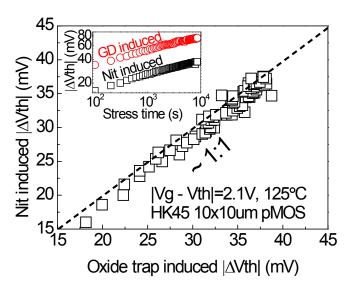

|   | 3.3.2 Contribution between interface states and Oxide traps                  | 80       |

|   | 3.4 Reliable NBTI Generated Defects' time exponent extraction                | 81       |

|   | 3.4.1 Existing values of NBTI Generated Defects' time exponent               |          |

|   | 3.4.2 Independent time exponent of Generated Defects                         | 82       |

|   | 3.4.3 Constant Vg and Constant Eox stress                                    | 84       |

|   | 3.4.4 Voltage dependence under different temperature                         |          |

|   | 3.4.5 Generated Defects under AC NBTI stress                                 | 88       |

|   | 3.4.6 Process dependence                                                     |          |

|   | 3.5 Generated Defects under PBTI stress                                      | 91       |

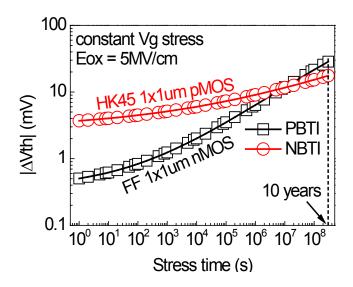

|   | 3.6 Evaluation of contribution from NBTI/PBTI Generated Defects at device    | lifetime |

|   | 92                                                                           |          |

|   | 3.7 Summary                                                                  | 93       |

| 4 | Pre_Existing defects under BTI stress                                        | 95       |

|   | 4.1 Introduction & Motivation                                                | 95       |

|   | 4.2 Two components in Pre_Existing defects                                   | 96       |

|   | 4.2.1 Energy profile evidence for two components in Pre_Existing defects     |          |

|   | 4.2.2 Principle for multi-DMP (m-DMP) technique                              | 98       |

|   | 4.2.3 As-grown Traps and Energy Alternating Defects separation               | 101      |

|   | 4.3 Temperature dependence of As-grown Traps and Energy Alternating Defec    | ts 103   |

|   | 4.4 Summary                                                                  |          |

| 5 | As-grown Generation (A-G) model under BTI stress                             |          |

|   | 5.1 Introduction & Motivation                                                |          |

|   | 5.2 A review of the A-G model                                                |          |

|   | 5.3 Application of the A-G model to NBTI                                     | 112      |

|   | 5.3.1 Generate Defects modelling                                             |          |

|   | 5.3.2 Pre_Existing defects modelling                                         | 113      |

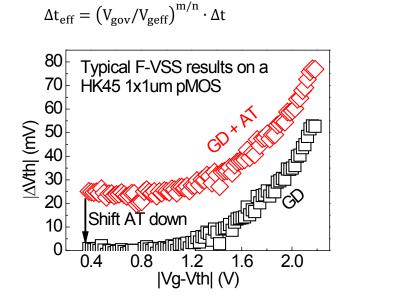

| 5.3.3 Fast-Voltage Step Stress technique for the A-G model 1<br>115 | parameter extraction   |

|---------------------------------------------------------------------|------------------------|

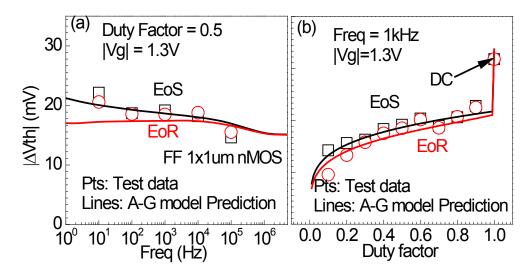

| 5.3.4 Experimental Validation under both DC & AC                    |                        |

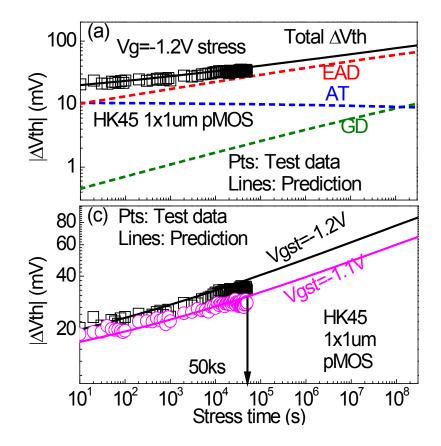

| 5.3.5 Evaluate each component contribution under use-bias at de     |                        |

| 5.4 Application of the A-G model to PBTI                            |                        |

| 5.5 Comparison of the A-G model with other models                   |                        |

| 5.6 Summary                                                         |                        |

| 6 Defect-induced Time Dependent Variability modelling               |                        |

| 6.1 Introduction & Motivation                                       |                        |

| 6.2 Deficiency of existing techniques for Time Dependent Variab     | ility characterization |

| 136                                                                 |                        |

| 6.3 Within Device Fluctuation (WDF) technique on nano-scale dev     | vices137               |

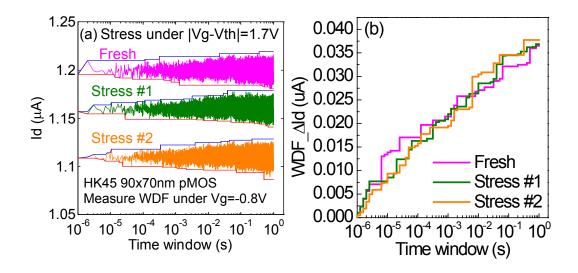

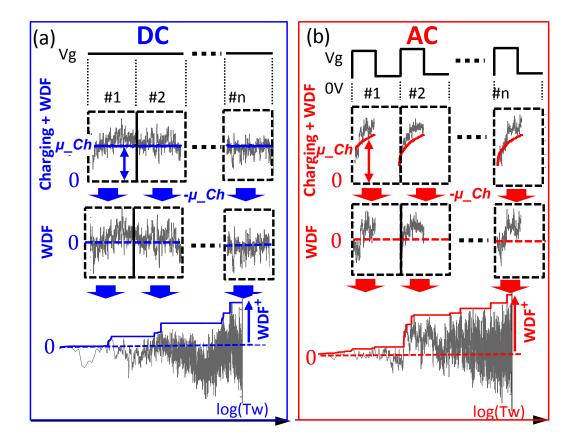

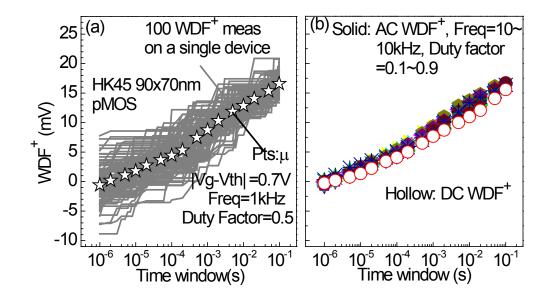

| 6.3.1 A review Within Device Fluctuation (WDF) technique            | 137                    |

| 6.3.2 Sampling rate dependence                                      | 142                    |

| 6.3.3 Stress dependence                                             | 142                    |

| 6.3.4 Frequency & Duty factor dependence                            | 143                    |

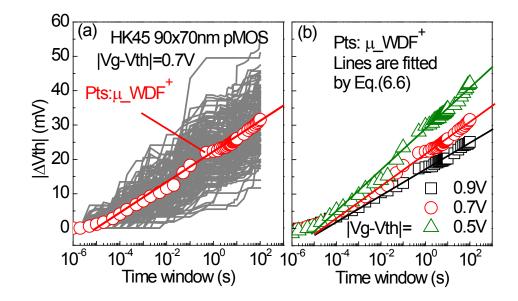

| 6.3.5 Within Device Fluctuation (WDF) modelling                     | 146                    |

| 6.4 Application of the A-G model on the averaged degradation        | 147                    |

| 6.4.1 Generated Defects modelling on nano-scale devices             | 148                    |

| 6.4.2 Pre_Existing defects modelling on nano-scale devices          | 151                    |

| 6.5 Device-to-Device Variability modelling                          |                        |

| 6.5.1 Device-to-Device Variability of WDF <sup>+</sup>              | 153                    |

| 6.5.2 Device-to-Device Variability of the averaged degradation.     |                        |

| 6.6 Time Dependent Variability modelling based on the A-G           |                        |

| Centric theory and experimental validation                          |                        |

| 6.7 Device & Circuit lifetime Prediction under use bias             |                        |

| 6.8 Summary                                                         |                        |

| 7 Conclusions and future work                                       |                        |

| 7.1 Conclusions                                                     |                        |

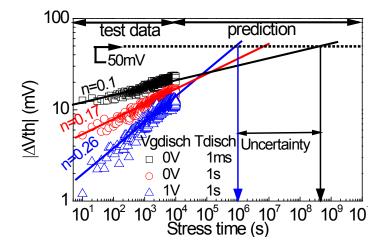

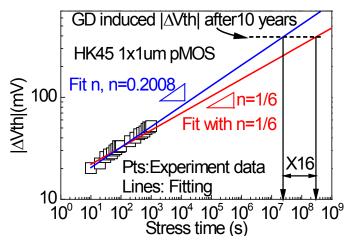

| 7.1.1 Conclusions on reliable time exponent extraction of long to   |                        |

| 7.1.2 Conclusions on the Fast-Voltage Step Stress acceleration t    |                        |

| 7.1.3 Conclusions on Pre_Existing defects                           |                        |

| 7.1.4 Conclusions on the test-proved A-G framework lifetime         |                        |

| scale devices                                                       |                        |

| 7.2 Future work                                                     |                        |

| 7.2.1 BTI and Hot Carrier Aging (HCA) coupling                      |                        |

| 7.2.2 Within Device Fluctuation (WDF) simulation                    |                        |

| 7.2.3 Circuit simulation                                            |                        |

| 8 References                                                        |                        |

# **1** Introduction of Bias Temperature Instability (BTI) Lifetime Prediction

### **1.1 A review of BTI lifetime prediction**

Nowadays electronic products are widely used in daily life from all aspects. Reliability is one of the most important parameters for electronic products. Product failures due to circuit malfunction can result in excessive warranty costs and severe brand damage to any integrated circuit company. In 2011, for example, Intel was about to launch their Sandy Bridge processor when a potential reliability problem was detected. The problem, which was not spotted during extensive functional testing, was a gradual performance reduction and even total failure of the serial-ATA channels in about 5% of the manufactured integrated circuits [1]. Unfortunately, this is not rare. A similar event also happened to Cisco, costing \$655 million to fix [2].

As semiconductor manufacturing technology node migrates, the complexity of circuits nowadays requires the reliability to be evaluated while design optimization before the fabrication. One example is the circuit operating voltage  $V_{dd}$  selection. Higher  $V_{dd}$  can enhance MOSFET drive current and increase the switching speed to achieve a higher performance, but the degradation will also be higher. To make a trade-off between performance and reliability, a lifetime prediction model becomes a prerequisite.

1

### 1.1.1 Introduction of BTI

Bias Temperature Instability (BTI) is a key reliability issue in MOSFET. It describes a phenomenon that degrades the performance of a device when a bias is applied on the gate of the MOSFET and turns on that channel. BTI on one hand, will cause device threshold voltage  $|V_{th}|$  to increase, resulting in a reduction of device driving current  $|I_d|$  (Fig. 1.1a) and circuit operating frequency; on the other hand, BTI will enhance the absolute "off" current  $|I_{doff}|$  (Fig. 1.1b) and Gate Leakage  $|I_g|$  (Fig. 1.1c), resulting in the increase of circuit power consumption. BTI is normally characterized by threshold voltage shift ( $|\Delta V_{th}|$ ) against stress time. Elevated temperature will accelerate BTI. 125°C is the temperature people normally used to do BTI tests, which is also used hereafter if not specified.

Fig. 1.1 MOSFET  $I_d$ - $V_g$  (IV) curves show both  $|V_{th}|$  (a) and  $|I_{d_off}|$  increases under NBTI stress. (c)  $I_g$ - $V_g$  measurements show gate leakage ( $I_g$ ) also increases.

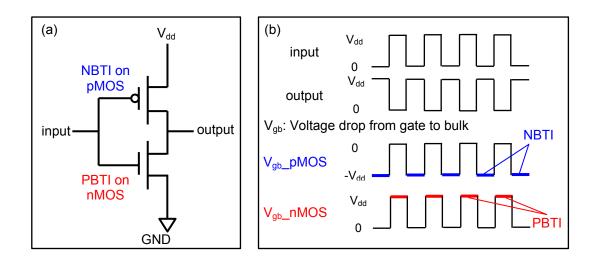

Most integrated circuits suffer from BTI degradation. A typical example is a Complementary Metal Oxide Semiconductor (CMOS) inverter, which is the basic logic cell in integrated circuits. Fig. 1.2 shows pMOS/nMOS suffers from Negative/Positive Bias Temperature Instability when the CMOS inverter is operating.

Fig. 1.2 (a) Illustration of the operation condition of a CMOS inverter in circuits. (b) With input 0/1 (GND/V<sub>dd</sub>), output is 1/0 (V<sub>dd</sub>/GND) and the pMOS/nMOS device (top/bottom) is under uniform negative/positive gate bias towards its bulk in the marked phases.

The complexity of circuit fabrication increases geometrically with MOSFET feature size scaling down and circuit integration goes up. Circuit designers need to consider the circuit lifetime as soon as they start to design the circuits before fabrication. One example is usebias  $V_{dd}$  selection. Higher  $V_{dd}$  means higher circuit performance, but meanwhile the degradation will also be higher and lifetime is sacrificed. To make a proper trade-off between performance and reliability, lifetime prediction is needed. As one of the most important reliability mechanism, BTI lifetime prediction becomes a necessity for industry.

### 1.1.2 Origin of BTI

BTI is caused by the creation or filling of traps in gate dielectric. The extra charges in gate dielectric will impose an inverted electric field in terms of gate voltage, resulting  $|V_{th}|$  to increase. Created traps will also assist carrier hopping thus  $|I_g|$  also increases.

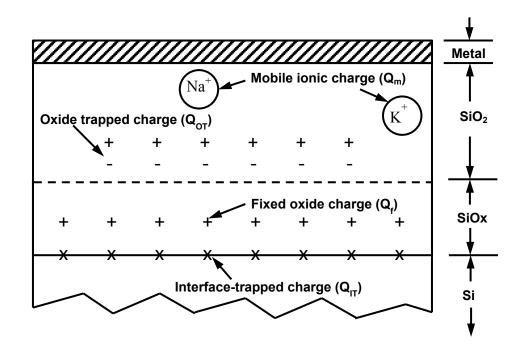

Traps and charges in gate dielectric are usually classified into four categories (Fig. 1.3), as suggested by B.E. Deal [3] in 1980. They are: 1). Interface states  $N_{IT}$  and trapped charges  $Q_{IT}$ , which are located at the Si-SiO<sub>2</sub> interface with energy states within the silicon forbidden bandgap and can exchange charges with silicon in a short time; Interface traps can possibly be produced by excess silicon (trivalent silicon), broken Si-H bonds, excess oxygen and impurities; 2). Fixed oxide charges  $Q_f$ , which are located at or near the

Fig. 1.3 Names and locations of charges associated with thermal oxidized silicon [3].

4

interface and are immobile under an applied electric field; 3). Oxide trapped charges  $Q_{OT}$ , which can be created, for example, by X-ray radiation or hot-electron injection; these traps are distributed inside the oxide layer; 4). Mobile ionic charges  $Q_m$ , such as sodium ions, which are mobile within the oxide under BTI stress condition.

When BTI was first observed in 1967 [4], it was mainly caused by ionic contamination [5, 6] and electrically active surface states passivation at Si-SiO<sub>2</sub> interface [7, 8] from the immature fabrication technology. With the development of semiconductor manufacturing [9-11], ionic contamination and pre-existing interface states can be well controlled, now it's mainly the creation of interface states and oxide traps that are responsible for BTI degradation.

With the scaling down of MOSFET feature size, the status of BTI compared to other reliability mechanisms has been changing at different stages. In the 1970s, Hot Carrier Aging (HCA) was the most important as circuits are driven by a high  $V_{dd}$ ; in 1980s with  $V_{dd}$  scaling down with feature size HCA was much alleviated, while the thin gate oxide makes Time Dependent Dielectric Breakdown (TDDB) start to be a major problem; in 2000s High- $\kappa$  material is widely used to suppress TDDB. High- $\kappa$  material can have the same amount of capacitance with a much larger thickness, TDDB is no longer a major problem then. But High- $\kappa$  material will enhance BTI degradation [12, 13], and BTI starts to become one of the most important sources of reliability concern [14, 15].

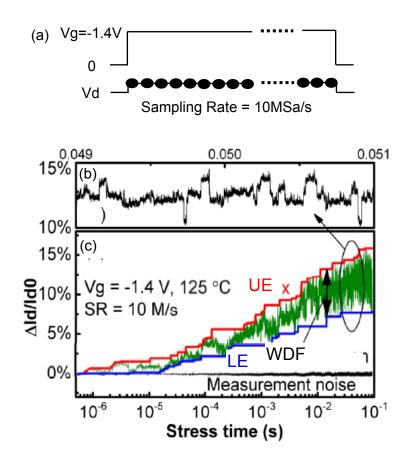

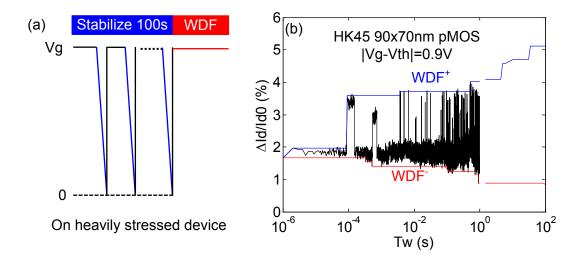

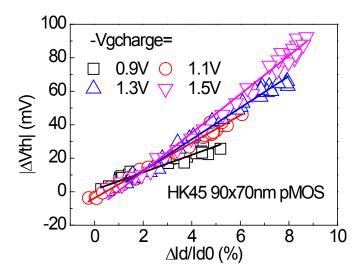

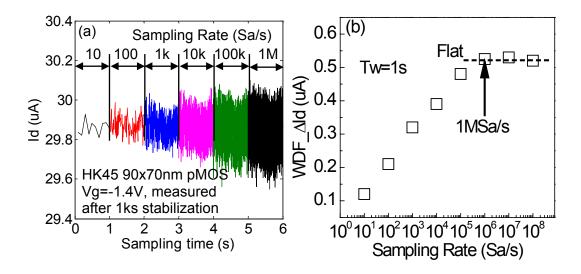

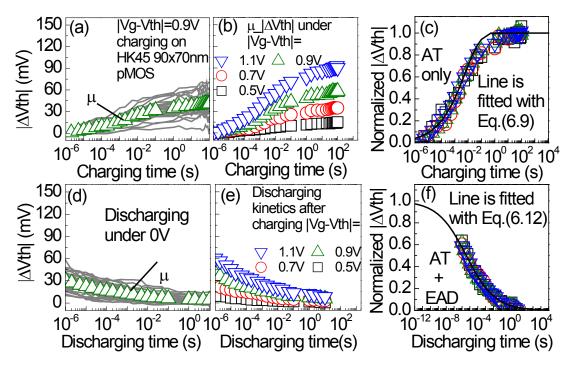

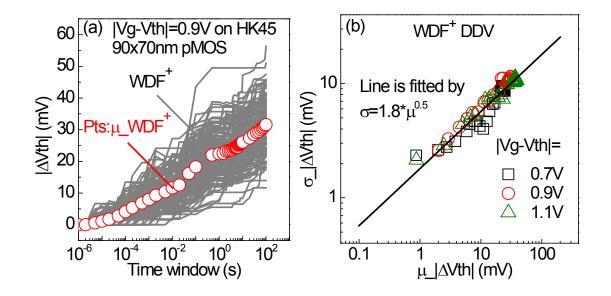

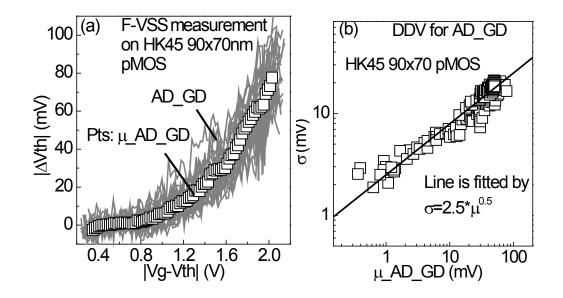

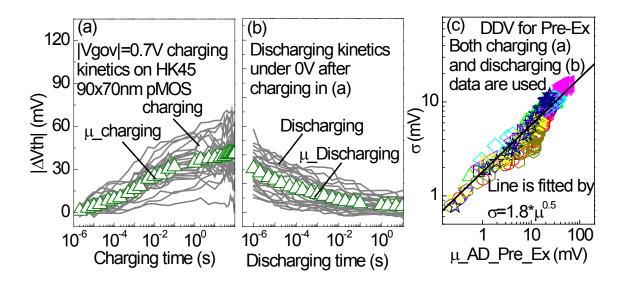

### 1.1.3 Accelerate characterization of BTI